# NEHRU COLLEGE OF ENGINEERING AND RESEARCH CENTRE (NAAC Accredited)

(Approved by AICTE, Affiliated to APJ Abdul Kalam Technological University, Kerala)

#### DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

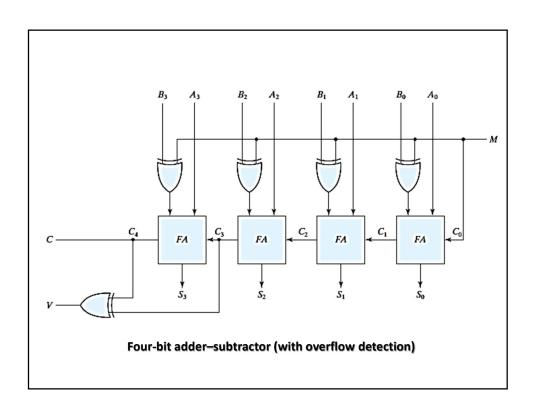

# **COURSE MATERIALS**

ECT 203: LOGIC CIRCUIT DESIGN

#### VISION OF THE INSTITUTION

To mould true citizens who are millennium leaders and catalysts of change through excellence in education.

### MISSION OF THE INSTITUTION

**NCERC** is committed to transform itself into a center of excellence in Learning and Research in Engineering and Frontier Technology and to impart quality education to mould technically competent citizens with moral integrity, social commitment and ethical values.

We intend to facilitate our students to assimilate the latest technological know-how and to imbibe discipline, culture and spiritually, and to mould them in to technological giants, dedicated research scientists and intellectual leaders of the country who can spread the beams of light and happiness among the poor and the underprivileged.

### ABOUT DEPARTMENT

♦ Established in: 2002

♦ Course offered: B.Tech in Electronics and Communication Engineering

M.Tech in VLSI

- ♦ Approved by AICTE New Delhi and Accredited by NAAC

- ♦ Affiliated to the A P J Abdul Kalam Technological University.

### DEPARTMENT VISION

Provide well versed, communicative Electronics Engineers with skills in Communication systems with corporate and social relevance towards sustainable developments through quality education.

#### **DEPARTMENT MISSION**

- 1) Imparting Quality education by providing excellent teaching, learning environment.

- 2) Transforming and adopting students in this knowledgeable era, where the electronic gadgets (things) are getting obsolete in short span.

- 3) To initiate multi-disciplinary activities to students at earliest and apply in their respective fields of interest later.

- 4) Promoting leading edge Research & Development through collaboration with academia & industry.

### PROGRAMME EDUCATIONAL OBJECTIVES

- PEO1. To prepare students to excel in postgraduate programmes or to succeed in industry / technical profession through global, rigorous education and prepare the students to practice and innovate recent fields in the specified program/ industry environment.

- PEO2. To provide students with a solid foundation in mathematical, Scientific and engineering fundamentals required to solve engineering problems and to have strong practical knowledge required to design and test the system.

- PEO3. To train students with good scientific and engineering breadth so as to comprehend, analyze, design, and create novel products and solutions for the real life problems.

- PEO4. To provide student with an academic environment aware of excellence, effective communication skills, leadership, multidisciplinary approach, written ethical codes and the life-long learning needed for a successful professional career.

### **PROGRAM OUTCOMES (POS)**

## **Engineering Graduates will be able to:**

- 1. **Engineering knowledge**: Apply the knowledge of mathematics, science, engineering fundamentals, and an engineering specialization to the solution of complex engineering problems.

- 2. **Problem analysis**: Identify, formulate, review research literature, and analyze complex engineering problems reaching substantiated conclusions using first principles of mathematics, natural sciences, and engineering sciences.

- 3. **Design/development of solutions**: Design solutions for complex engineering problems and design system components or processes that meet the specified needs with appropriate consideration for the public health and safety, and the cultural, societal, and environmental considerations.

- 4. **Conduct investigations of complex problems**: Use research-based knowledge and research methods including design of experiments, analysis and interpretation of data, and synthesis of the information to provide valid conclusions.

- 5. **Modern tool usage**: Create, select, and apply appropriate techniques, resources, and modern engineering and IT tools including prediction and modeling to complex engineering activities with an understanding of the limitations.

- 6. **The engineer and society**: Apply reasoning informed by the contextual knowledge to assess societal, health, safety, legal and cultural issues and the consequent responsibilities relevant to the professional engineering practice.

- 7. **Environment and sustainability**: Understand the impact of the professional engineering solutions in societal and environmental contexts, and demonstrate the knowledge of, and need for sustainable development.

- 8. **Ethics**: Apply ethical principles and commit to professional ethics and responsibilities and norms of the engineering practice.

- 9. **Individual and team work**: Function effectively as an individual, and as a member or leader in diverse teams, and in multidisciplinary settings.

- 10. **Communication**: Communicate effectively on complex engineering activities with the engineering community and with society at large, such as, being able to comprehend and write effective reports and design documentation, make effective presentations, and give and receive clear instructions.

- 11. **Project management and finance**: Demonstrate knowledge and understanding of the engineering and management principles and apply these to one's own work, as a member and leader in a team, to manage projects and in multidisciplinary environments.

- 12. **Life-long learning**: Recognize the need for, and have the preparation and ability to engage in independent and life-long learning in the broadest context of technological change.

## PROGRAM SPECIFIC OUTCOMES (PSO)

**PSO1**: Facility to apply the concepts of Electronics, Communications, Signal processing, VLSI, Control systems etc., in the design and implementation of engineering systems.

**PSO2**: Facility to solve complex Electronics and communication Engineering problems, using latest hardware and software tools, either independently or in team.optimization.

## **SYLLABUS**

| ECT 203 | LOGIC CIRCUIT DESIGN | CATEGORY | L | T | P | CREDIT |

|---------|----------------------|----------|---|---|---|--------|

|         |                      | PCC      | 3 | 1 | 0 | 4      |

**Preamble:** This course aims to impart the basic knowledge of logic circuits and enable students to apply it to design a digital system.

**Prerequisite:** EST130 Basics of Electrical and Electronics Engineering

**Course Outcomes:** After the completion of the course the student will be able to

| CO 1 | Explain the elements of digital system abstractions such as digital representations of |

|------|----------------------------------------------------------------------------------------|

|      | information, digital logic and Boolean algebra                                         |

| CO 2 | Create an implementation of a combinational logic function described by a truth table  |

|      | using and/or/inv gates/ muxes                                                          |

| CO 3 | Compare different types of logic families with respect to performance and efficiency   |

| CO 4 | Design a sequential logic circuit using the basic building blocks like flip-flops      |

| CO 5 | Design and analyze combinational and sequential logic circuits through gate level      |

|      | Verilog models.                                                                        |

# Mapping of course outcomes with program outcomes

|      | РО | PO 2 | PO 3 | PO 4 | PO 5 | PO 6 | PO 7 | PO 8 | PO 9 | РО | РО | PO 12 |

|------|----|------|------|------|------|------|------|------|------|----|----|-------|

|      | 1  |      |      |      |      |      |      |      |      | 10 | 11 |       |

| CO 1 | 3  | 3    |      |      |      |      |      |      |      |    |    |       |

| CO 2 | 3  | 3    | 3    |      |      |      |      |      |      |    |    |       |

| CO 3 | 3  | 3    |      |      |      |      |      |      |      |    |    |       |

| CO 4 | 3  | 3    | 3    |      |      |      |      |      |      |    |    |       |

| CO 5 | 3  | 3    | 3    |      | 3    |      |      |      |      |    |    |       |

#### **Assessment Pattern**

| Bloom's Category | Bloom's Category Continuous Assessment |    | End Semester Examination |

|------------------|----------------------------------------|----|--------------------------|

|                  | 1                                      | 2  |                          |

| Remember         | 10                                     | 10 | 10                       |

| Understand       | 20                                     | 20 | 20                       |

| Apply            | 20                                     | 20 | 70                       |

| Analyse          |                                        |    |                          |

| Evaluate         |                                        |    |                          |

| Create           |                                        |    |                          |

#### Mark distribution

| <b>Total Marks</b> | CIE | ESE | ESE Duration |

|--------------------|-----|-----|--------------|

| 150                | 50  | 100 | 3 hours      |

## **Continuous Internal Evaluation Pattern:**

Attendance : 10 marks

Continuous Assessment Test (2 numbers) : 25 marks

Course project : 15 marks

## **Course Level Assessment Questions**

# **Course Outcome 1 (CO1): Number Systems and Codes**

- 1. Consider the signed binary numbers A = 01000110 and B = 11010011 where B is in 2's complement form. Find the value of the following mathematical expression (i) A + B (ii) A B

- 2. Perform the following operations (i)D9CE<sub>16</sub>-CFDA<sub>16</sub> (ii) 6575<sub>8</sub>-5732<sub>8</sub>

- 3. Convert decimal 6,514 to both BCD and ASCII codes. For ASCII, an even parity bit is to be appended at the left.

#### Course Outcome 2 (CO2): Boolean Postulates and combinational circuits

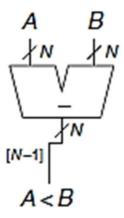

- 1. Design a magnitude comparator to compare two 2-bit numbers  $A = A_1A_0$  and  $B = B_1B_0B$

- 2. Simplify using K-map  $F(a,b,c,d) = \sum m (4,5,7,8,9,11,12,13,15)$

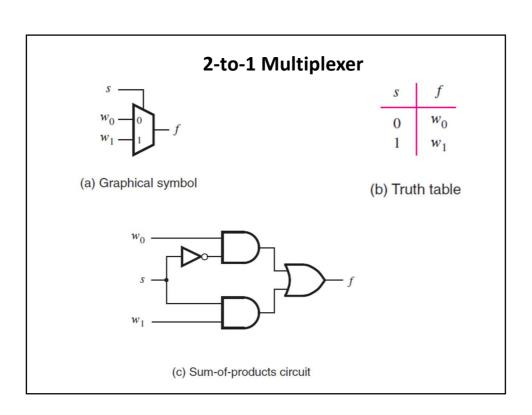

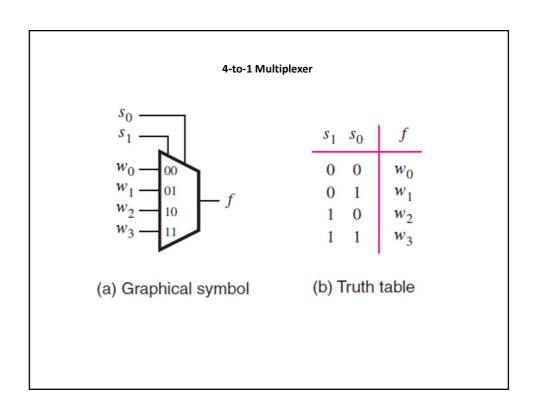

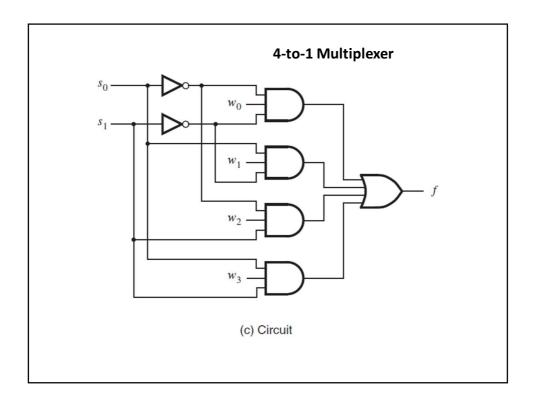

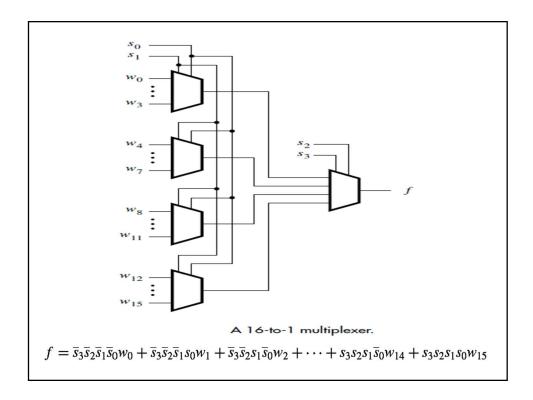

- 3. Explain the operation of a 8x1 multiplexer and implement the following using an 8x1 multiplexer F(A, B, C, D) =  $\Sigma$  m (0, 1, 3, 5, 6, 7, 8, 9, 11, 13, 14)

## **Course Outcome 3 (CO3): Logic families and its characteristics**

- 1. Define the terms noise margin, propagation delay and power dissipation of logic families. Compare TTL and CMOS logic families showing the values of above mentioned terms.

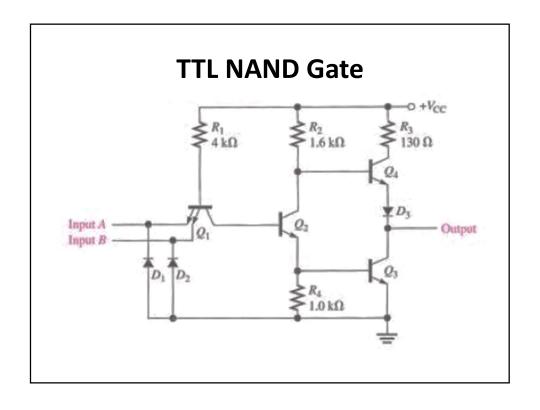

- 2. Draw the circuit and explain the operation of a TTL NAND gate

- 3. Compare TTL, CMOS logic families in terms of fan-in, fan-out and supply voltage

# Course Outcome 4 (CO4): Sequential Logic Circuits

- 1. Realize a T flip-flop using NAND gates and explain the operation with truth table, excitation table and characteristic equation

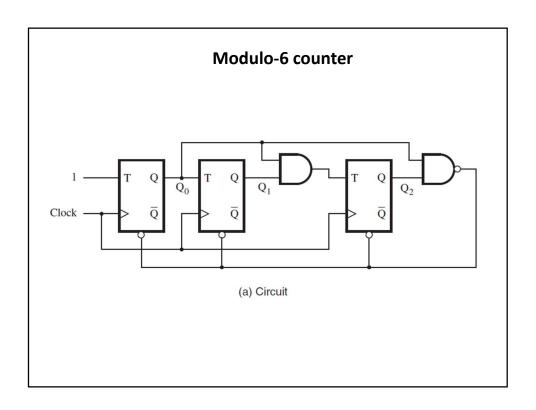

- 2. Explain a MOD 6 asynchronous counter using JK Flip Flop

- 3. Draw the logic diagram of 3 bit PIPO shift register with LOAD/SHIFT control and explain its working

## Course Outcome 5 (CO5): Logic Circuit Design using HDL

- 1. Design a 4-to-1 mux using gate level Verilog model.

- 2. Design a verilog model for a half adder circuit. Make a one bit full adder by connecting two half adder models.

- 3. Compare concurrent signal assignment versus sequential signal assignment.

## **Syllabus**

# **Module 1: Number Systems and Codes:**

Binary and hexadecimal number systems; Methods of base conversions; Binary and hexadecimal arithmetic; Representation of signed numbers; Fixed and floating point numbers; Binary coded decimal codes; Gray codes; Excess 3 code. Alphanumeric codes: ASCII. Basics of verilog -- basic language elements: identifiers, data objects, scalar data types, operators.

#### **Module 2: Boolean Postulates and Fundamental Gates**

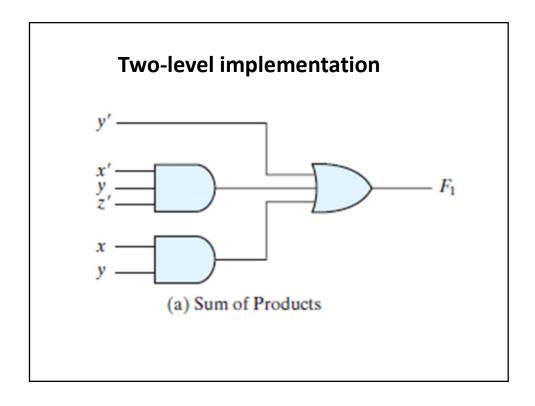

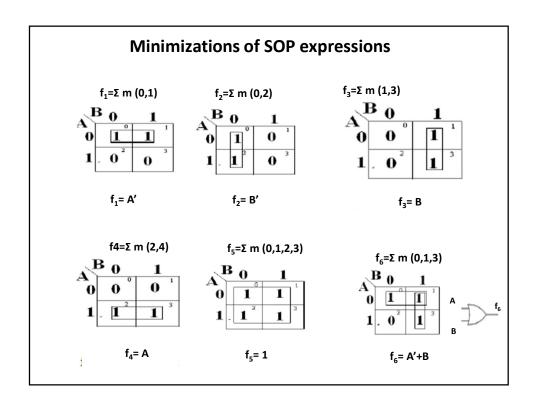

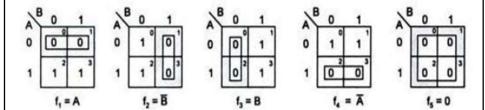

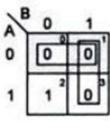

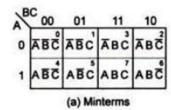

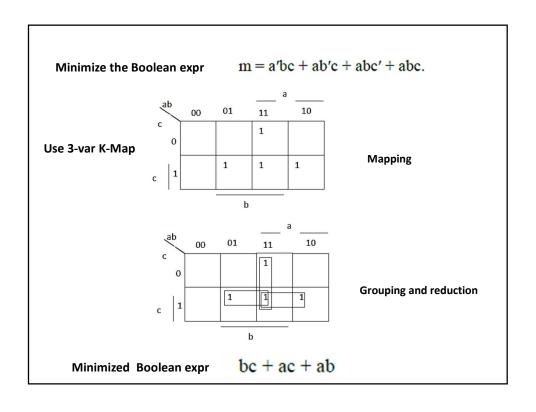

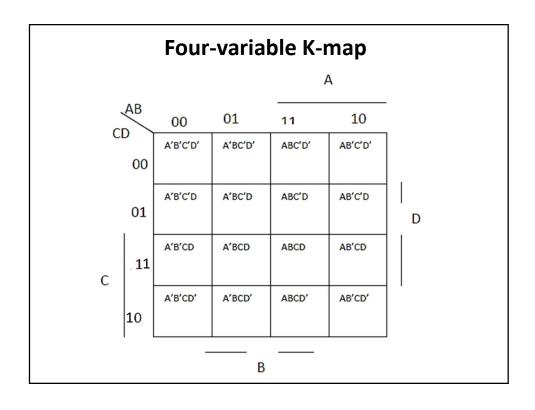

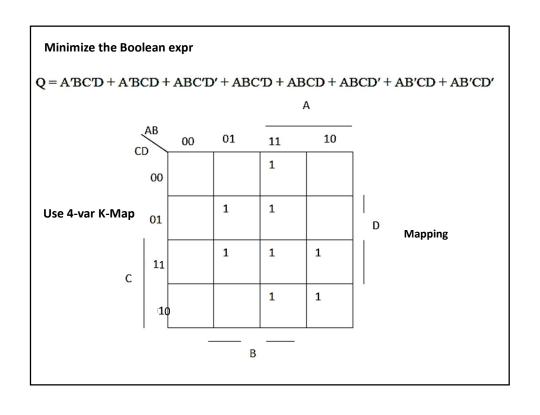

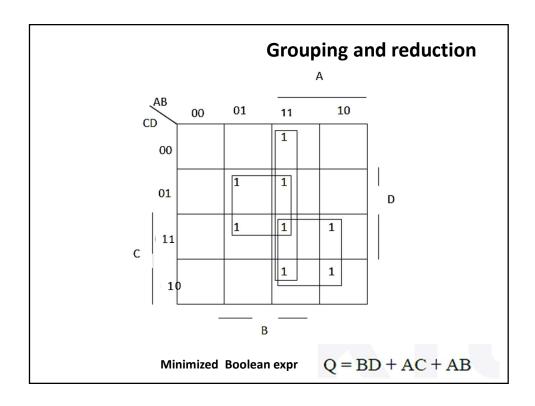

Boolean postulates and laws – Logic Functions and Gates De-Morgan's Theorems, Principle of Duality, Minimization of Boolean expressions, Sum of Products (SOP), Product of Sums (POS), Canonical forms, Karnaugh map Minimization. Modeling in verilog, Implementation of gates with simple verilog codes.

## **Module 3: Combinatorial and Arithmetic Circuits**

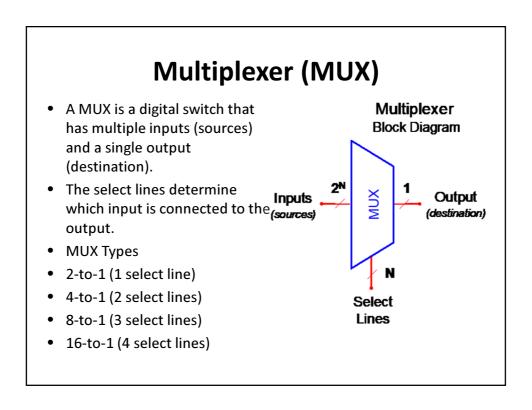

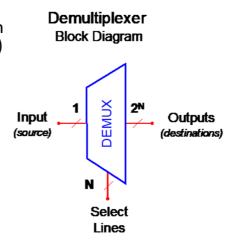

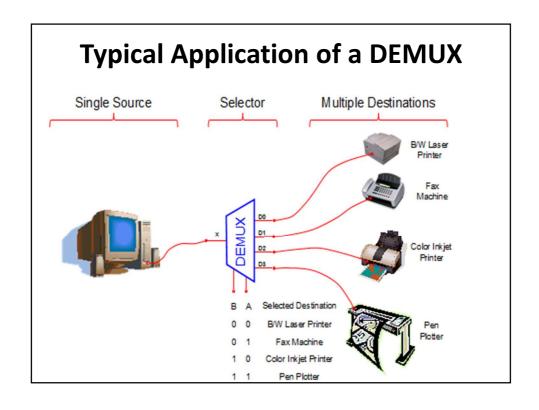

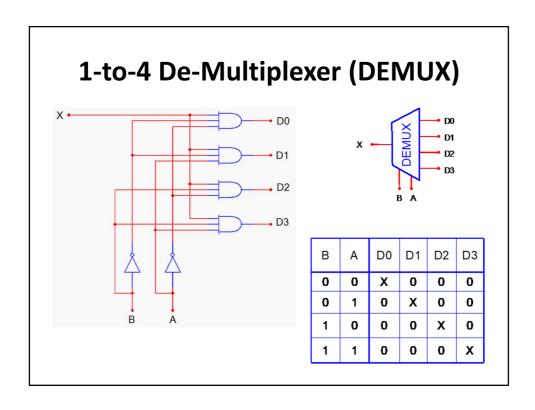

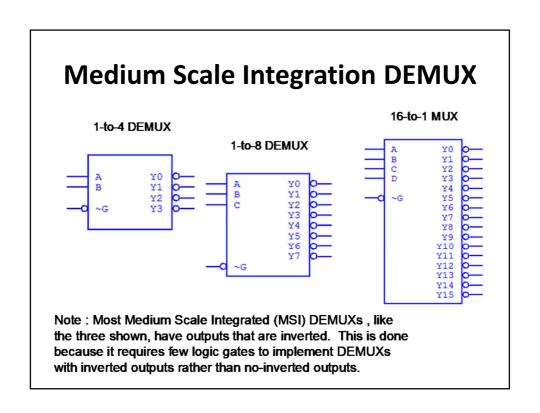

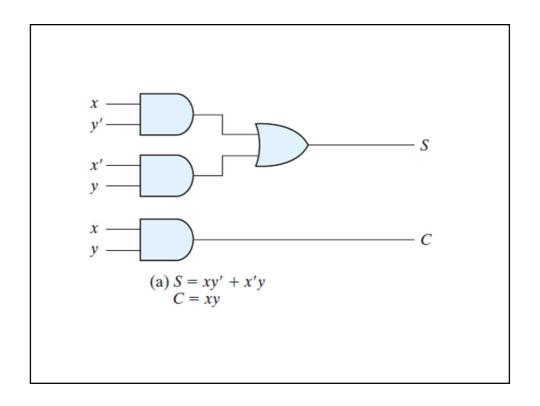

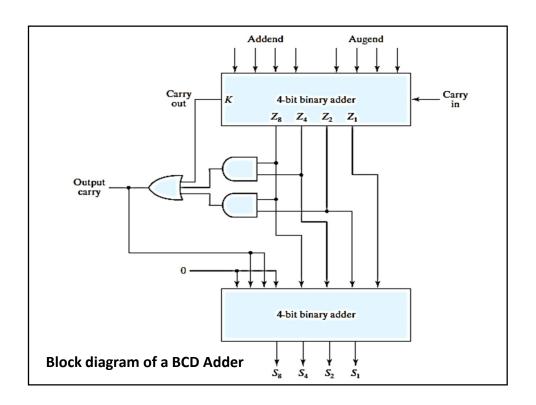

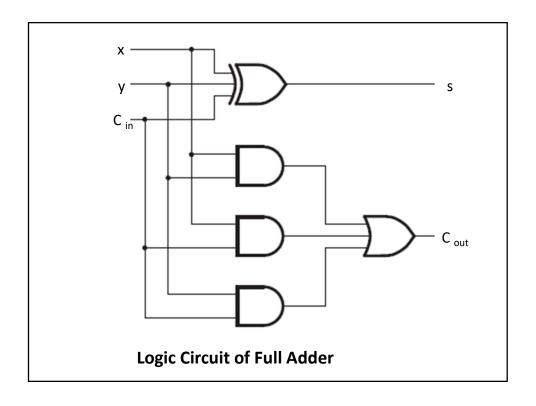

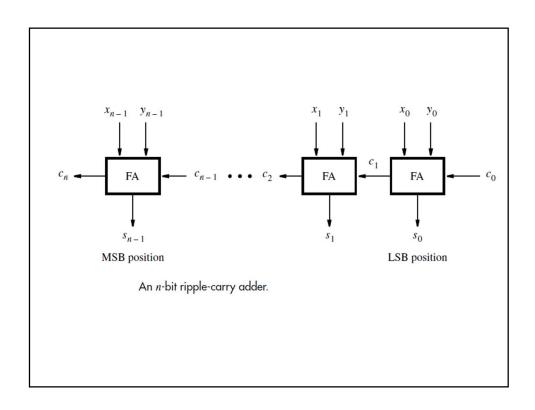

Combinatorial Logic Systems - Comparators, Multiplexers, Demultiplexers, Encoder, Decoder. Half and Full Adders, Subtractors, Serial and Parallel Adders, BCD Adder. Modeling and simulation of combinatorial circuits with verilog codes at the gate level.

# **Module 4: Sequential Logic Circuits:**

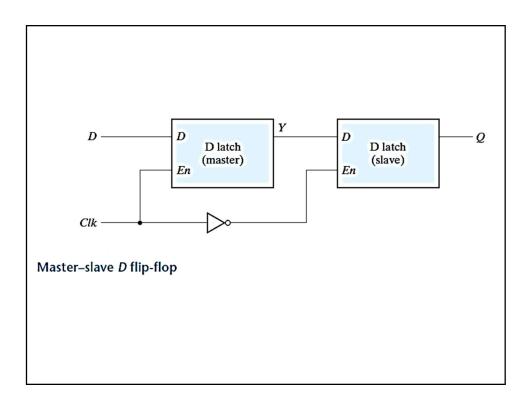

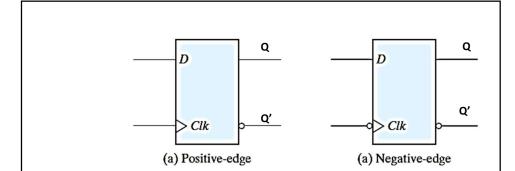

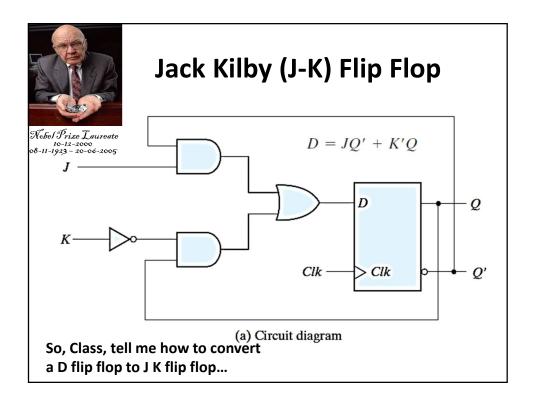

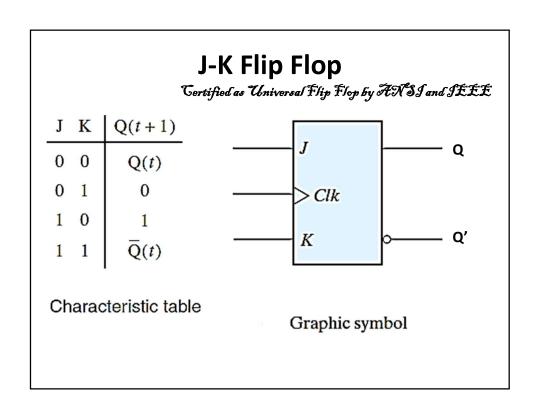

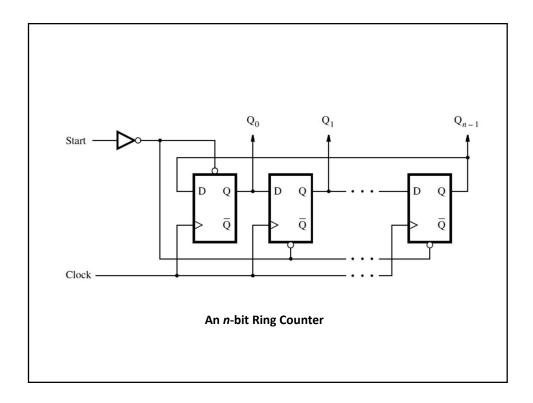

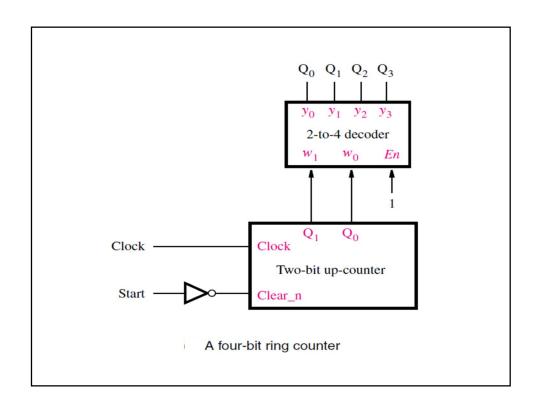

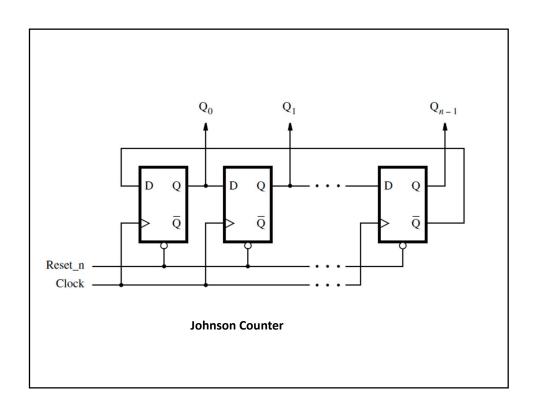

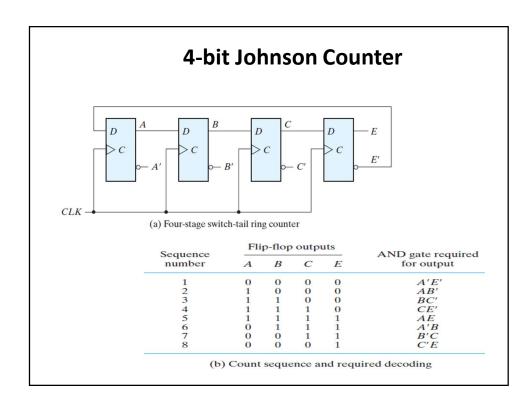

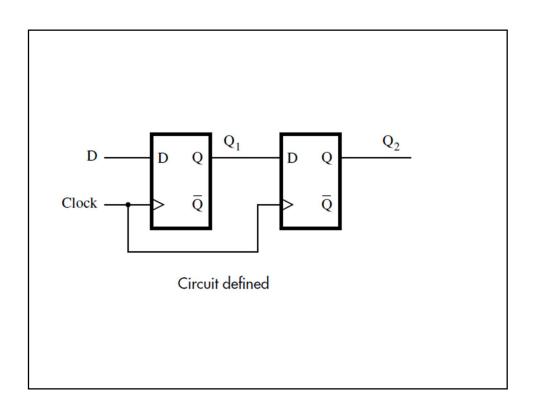

Building blocks like S-R, JK and Master-Slave JK FF, Edge triggered FF, Conversion of Flipflops, Excitation table and characteristic equation. Implementation with verilog codes. Ripple and Synchronous counters and implementation in verilog, Shift registers-SIPO, SISO, PISO, PIPO. Shift Registers with parallel Load/Shift, Ring counter and Johnsons counter. Asynchronous and Synchronous counter design, Mod N counter. Modeling and simulation of flipflops and counters in verilog.

## **Module 5: Logic families and its characteristics:**

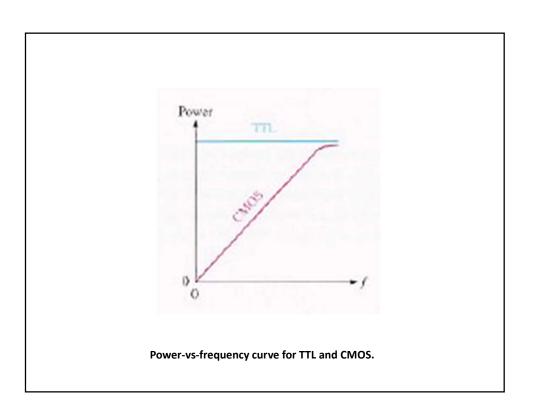

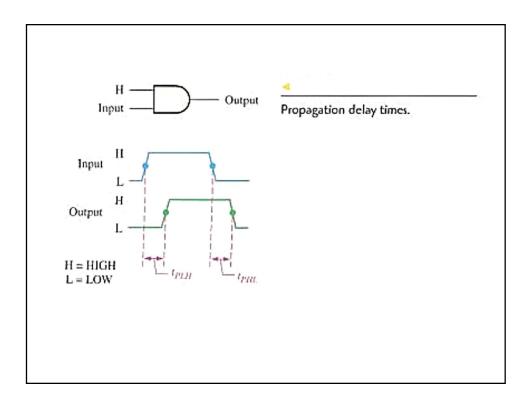

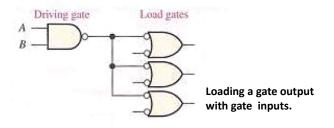

TTL, ECL, CMOS - Electrical characteristics of logic gates – logic levels and noise margins, fan-out, propagation delay, transition time, power consumption and power-delay product. TTL inverter - circuit description and operation; CMOS inverter - circuit description and operation; Structure and operations of TTL and CMOS gates; NAND in TTL and CMOS, NAND and NOR in CMOS.

#### **Text Books**

- 1. Mano M.M., Ciletti M.D., "Digital Design", Pearson India, 4th Edition. 2006

- 2. D.V. Hall, "Digital Circuits and Systems", Tata McGraw Hill, 1989

- 3. S. Brown, Z. Vranesic, "Fundamentals of Digital Logic with Verilog Design", McGraw Hill

- 4. Samir Palnikar"Verilog HDL: A Guide to Digital Design and Syntheis", Sunsoft Press

- 5. R.P. Jain, "Modern digital Electronics", Tata McGraw Hill, 4th edition, 2009

#### **Reference Books**

- 1. W.H. Gothmann, "Digital Electronics An introduction to theory and practice", PHI, 2<sup>nd</sup> edition ,2006

- 2. Wakerly J.F., "Digital Design: Principles and Practices," Pearson India, 4th 2008

- 3. A. Ananthakumar ,"Fundamentals of Digital Circuits", Prentice Hall, 2nd edition, 2016

- 4. Fletcher, William I., An Engineering Approach to Digital Design, 1st Edition, Prentice Hall India, 1980

#### **Course Contents and Lecture Schedule**

| No  | Topic No. of Le                                                         |          |   |  |

|-----|-------------------------------------------------------------------------|----------|---|--|

| 1   | Number Systems and Codes:                                               |          |   |  |

| 1.1 | Binary, octal and hexadecimal number systems; Methods of base           |          | 2 |  |

|     | conversions;                                                            |          |   |  |

| 1.2 | Binary, octal and hexadecimal arithmetic;                               |          |   |  |

| 1.3 | Representation of signed numbers; Fixed and floating point numbers;     |          |   |  |

| 1.4 | Binary coded decimal codes; Gray codes; Excess 3 code:                  |          |   |  |

| 1.5 | Error detection and correction codes - parity check codes and H         | amming   | 3 |  |

|     | code-Alphanumeric codes:ASCII                                           |          |   |  |

| 1.6 | Verilog basic language elements: identifiers, data objects, scalar data | a types, | 2 |  |

|     | operators                                                               |          |   |  |

|     |                                                                         |          |   |  |

| 2   |                                                                         |          |   |  |

| 2   | <b>Boolean Postulates and Fundamental Gates:</b>                        |          |   |  |

| 2.1 | Boolean postulates and laws – Logic Functions and Gates, De-Morg        | an's     | 2 |  |

|     | Theorems, Principle of Duality                                          |          |   |  |

| 2.2 | Minimization of Boolean expressions, Sum of Products (SOP), Prod        | uct of   | 2 |  |

|     | Sums (POS)                                                              |          |   |  |

| 2.3 | Canonical forms, Karnaugh map Minimization                                                                                                                                        | 1 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

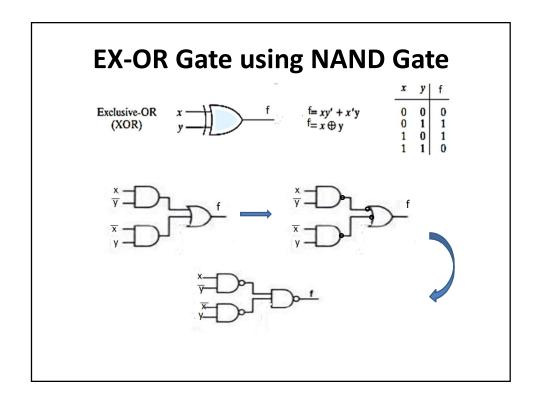

| 2.4 | Gate level modelling in Verilog: Basic gates, XOR using NAND and NOR                                                                                                              | 2 |

| 3   | Combinatorial and Arithmetic Circuits                                                                                                                                             |   |

| 3.1 | Combinatorial Logic Systems - Comparators, Multiplexers, Demultiplexers                                                                                                           | 2 |

| 3.2 | Encoder, Decoder, Half and Full Adders, Subtractors, Serial and Parallel Adders, BCD Adder                                                                                        | 3 |

| 3.3 | Gate level modelling combinational logic circuits in Verilog: half adder, full adder, mux, demux, decoder, encoder                                                                | 3 |

| 4   | Sequential Logic Circuits:                                                                                                                                                        |   |

| 4.1 | Building blocks like S-R, JK and Master-Slave JK FF, Edge triggered FF                                                                                                            | 2 |

| 4.2 | Conversion of Flipflops, Excitation table and characteristic equation.                                                                                                            | 1 |

| 4.3 | Ripple and Synchronous counters, Shift registers-SIPO.SISO,PISO,PIPO                                                                                                              | 2 |

| 4.4 | Ring counter and Johnsons counter, Asynchronous and Synchronous counter design                                                                                                    | 3 |

| 4.5 | Mod N counter, Random Sequence generator                                                                                                                                          | 1 |

| 4.6 | Modelling sequential logic circuits in Verilog: flipflops, counters                                                                                                               | 2 |

| 5   | Logic families and its characteristics:                                                                                                                                           |   |

| 5.1 | TTL,ECL,CMOS- Electrical characteristics of logic gates – logic levels and noise margins, fan-out, propagation delay, transition time, power consumption and power-delay product. | 3 |

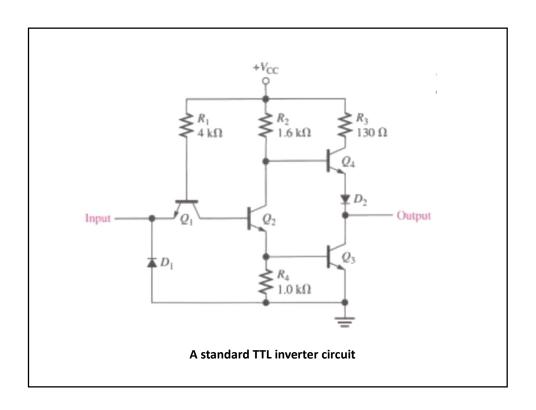

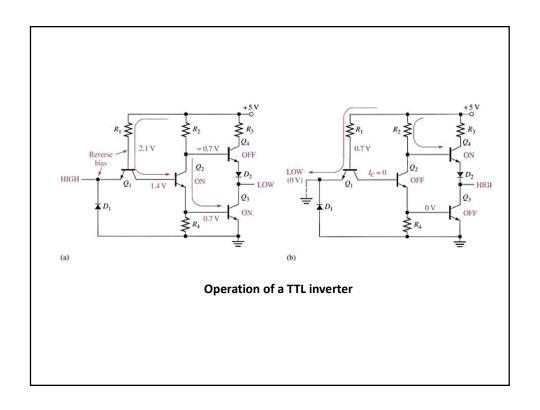

| 5.2 | TTL inverter - circuit description and operation                                                                                                                                  | 1 |

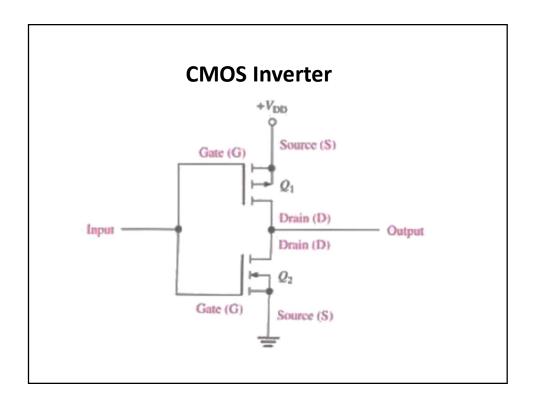

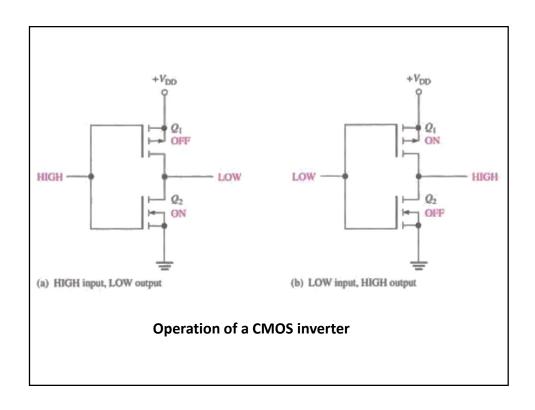

| 5.3 | CMOS inverter - circuit description and operation                                                                                                                                 | 1 |

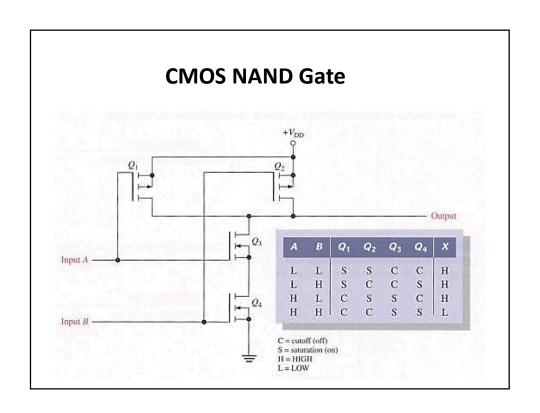

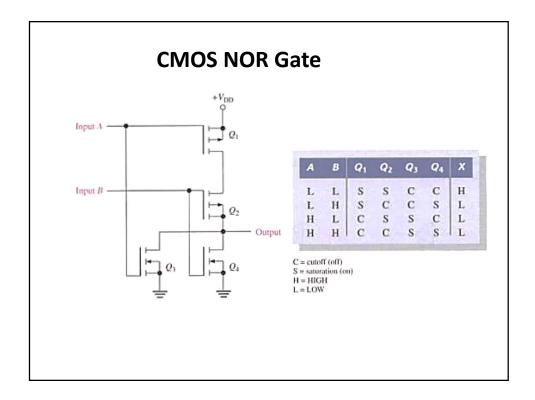

| 5.4 | Structure and operations of TTL and CMOS gates; NAND in TTL, NAND and NOR in CMOS.                                                                                                | 2 |

|     |                                                                                                                                                                                   |   |

## **QUESTION BANK**

# Module-1

- 1. Perform inter-conversions of the following:

- (a) AC0BFE<sub>16</sub> to Binary, Octal and Decimal

- (b) 775048 to Binary, Hexadecimal and Decimal

- (c) 111012 to Octal, Hexadecimal and Decimal

- (d) 7750410 to Binary, Hexadecimal and Octal

- (e) 7750410 to BCD 8421 and 2421

- (f) 137<sub>10</sub> to IEEE 754 Floating point number

- 2. Perform the subtraction of 65<sub>10</sub> from 110<sub>10</sub> using 2's complement arithmetic on 8-bit signed numbers and validate your answer.

- 3. Verify the following Verilog relational statement:

Given A, B, C, and D are operands, show with steps, Given that A=110, B=111, C=011000, D=111011

- 4. Show the floating-point representation of the decimal number 228, in version-1, version-2 and IEEE 754 notation.

- 5. Represent decimal number 228 using excess-3 code.

- 6. Explain with the aid of examples the 8421, 2421, Excess-3 and Gray Code. State which are weighted codes and unweighted codes.

- 7. Add the numbers FADE.BEE16 and BAD.FAB16 using hexadecimal arithmetic.

- 8. Explain the Data types in Verilog with examples.

- 9. Show the floating-point representation of the decimal number 232, in version-1, version-2 and IEEE 754 notation.

- 10. Add the numbers DEAD.BEEF16 and 100011.1010012 using hex arithmetic.

- 11. Add the numbers 677.4328 and 333.1238 using octal arithmetic with the aid of octal number line.

- 12. Explain the operation of each of the Verilog statements given below:

```

reg [7:0] b= 8'hA3;

{Carry, Sum} = a+ b;

integer signed a= 16'hBEEF;

```

- 13. Show the floating-point representation of the decimal number 238, in version-1, version-2 and IEEE 754 notation.

- 14. State what is Gray code? Draw the 4-bit Gray code representation. Provide the applications.

- 15. Explain about use of Parity bits for error detection.

- 16. Perform the following additions using bcd arithmetic and validate your answer: Add 12345 and 7234.

# **Module-2**

- 1. State De Morgan's Theorem and the rules. Apply the theorem as many times as needed to obtain the complement of the following function in standard canonical form: f' = (x'.y. z' + x'.y'.z)'

- 2. Explain the Principle of Duality with the aid of examples.

- 3. State and prove the Involution Theorem and the Absorption Theorem.

- **4.** State and prove the Associative Theorem and the Idempotent Theorem.

- **5.** What is a Truth Table? With the aid of Truth Table prove the De Morgan's Theorem.

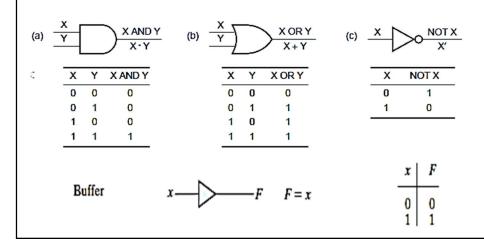

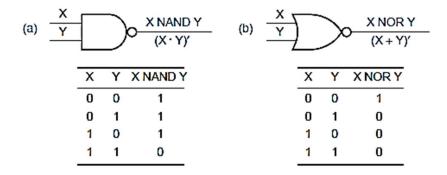

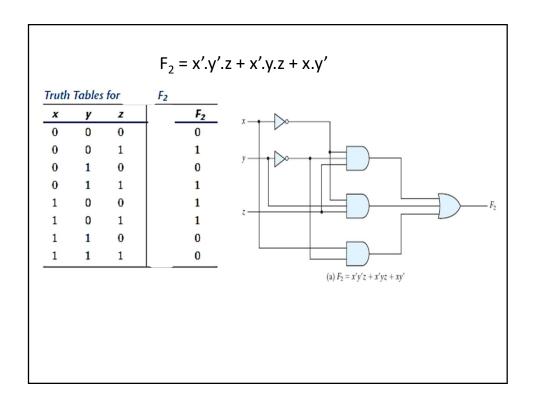

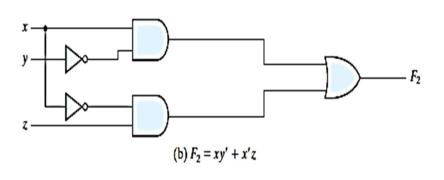

- **6.** Examine the different sets of Logic Gates with the aid of symbol, function and truth table.

- 7. Compare and contrast Buffer gate and Invertor gate.

- **8.** Decompose the Exclusive OR Function using universal gates with the aid of truth table, logic diagram and modified logic diagram. Write Verilog program for the result.

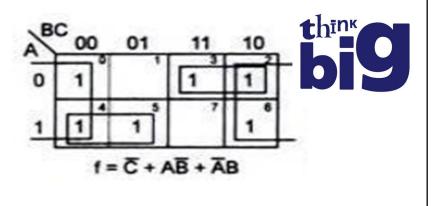

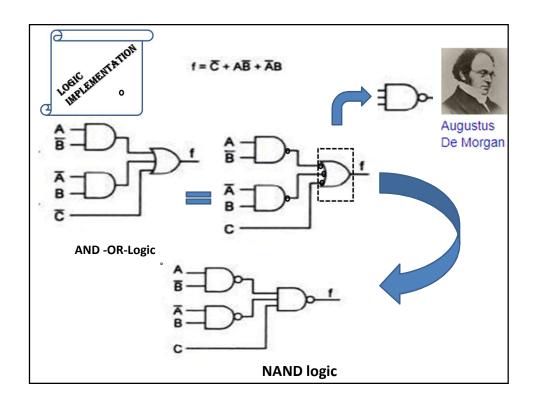

- **9.** Simplify the following Boolean expression using appropriate Karnaugh Map and provide the logic implementation of the minimized expression using gates.

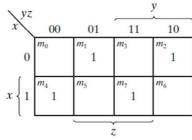

$$f(A, B, C, D) = \sum m(4, 5, 7, 8, 9, 11, 12, 13, 15)$$

- **10.** Construct the Verilog program module for the implementation in Q.9 and carefully provide comments for each line of the code.

- **11.** Explain the standard canonical forms for representing Boolean functions with the aid of two examples each.

- **12.** Explain the meaning of Literal, Minterm, Maxterm, Don't Care term, SOP and POS. Give examples to support your answers.

- **13.** Simplify the following Boolean expression using appropriate Karnaugh Map and provide the logic implementation of the minimized expression using <u>universal gates</u> with the aid of De Morgan's laws.

$$f=\sum m(0,2,3,4,5,6)$$

- **14.** Construct the Verilog program module for the above implementation in Q.13 and carefully provide comments for each line of the code.

- **15.** Decompose the Exclusive NOR Function using universal gates with the aid of truth table, logic diagram and modified logic diagram. Write Verilog program for the result.

- **16.** State De Morgan's Theorem and the rules. Apply the theorem as many times as needed to obtain the complement of the following function in standard canonical form:

$$f_2' = [(x.(y'.z' + y.z)]'$$

**17.** Simplify the following Boolean expression using appropriate Karnaugh Map and provide the logic implementation of the minimized expression using <u>universal gates</u> with the aid of De Morgan's laws.

$$\pi$$

M (0,3,5,6,7).

- **18.** Construct the Verilog program module for the above implementation in Q.17 and carefully provide comments for each line of the code.

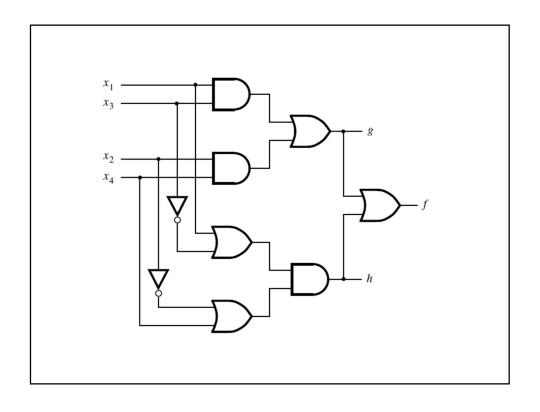

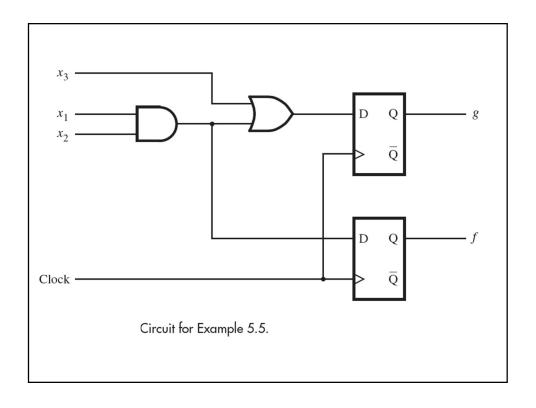

- 19. Write a well commented Verilog program for a circuit that has four input signals,  $x_1$ ,  $x_2$ ,  $x_3$ , and  $x_4$ , and three output signals, f, g, and h, and implements the logic functions:

$$g = x_1.x_3 + x_2.x_4$$

$h = (x_1 + x_3')(x_2' + x_4)$

$f = g + h$

**20.** Obtain the complement of the following function in standard canonical form by applying the De Morgan's rule as many times as needed, as well as Principle of Duality:

$$f_1 = (x + y + z)(x + y' + z)(x' + y + z')(x' + y' + z)$$

- **21.** Construct an XOR gate using NAND gates and perform gate level modeling using Verilog.

- 22. Construct an XOR gate using NOR gates and perform gate level modeling using Verilog.

- **23.** Repeat the above for XNOR Gate.

# Module-3 (Part-1)

- 1. State what is meant by a Combinational circuit? Draw a generic block diagram. Give four examples.

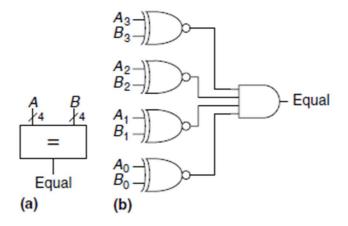

- **2.** Analyze the Comparator circuits with the aid of graphic symbol and logic implementations.

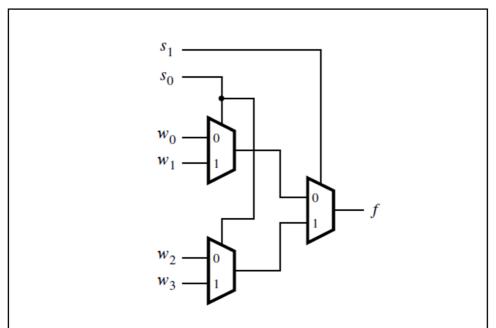

- **3.** Define the Multiplexer function. Analyze the 4:1 MUX with the aid of graphic symbol, truth table and logic implementation.

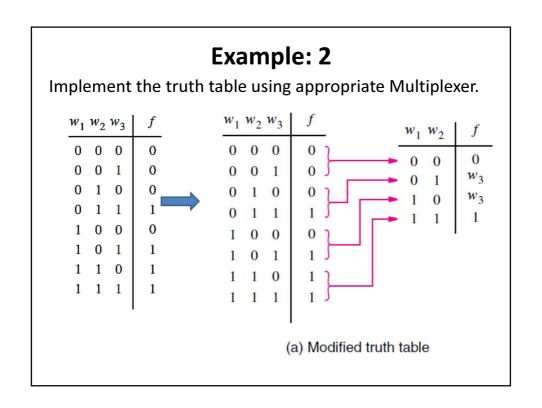

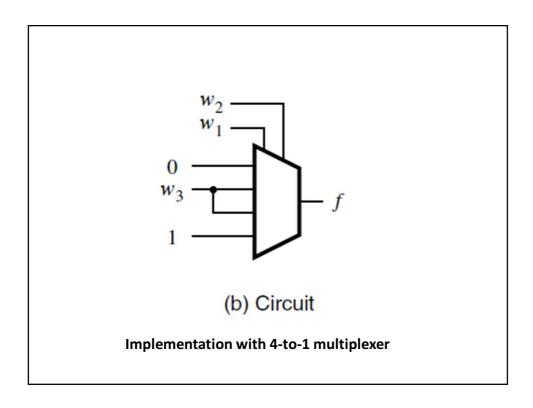

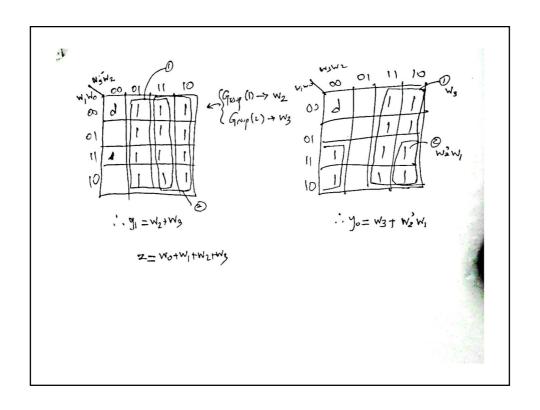

- **4.** Implement the following Boolean function using an appropriate Multiplexer after judicious manipulation of the original truth table.

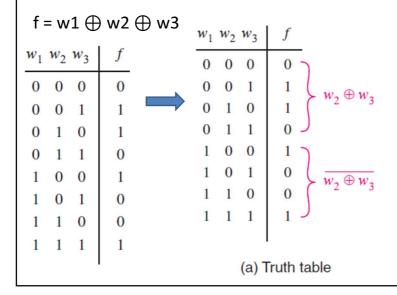

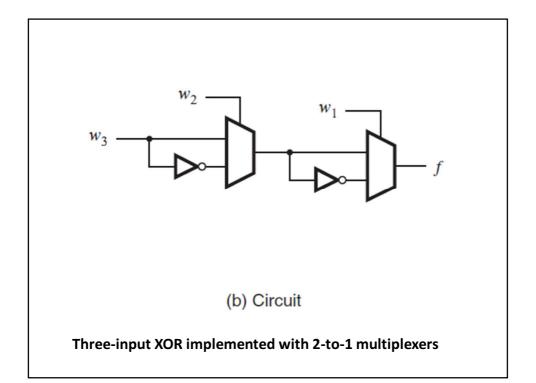

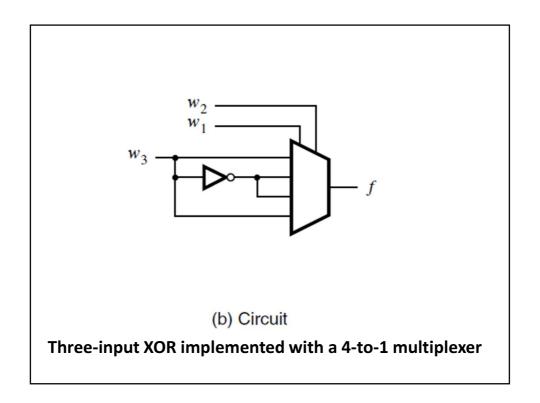

$f = w1 \oplus w2 \oplus w3$

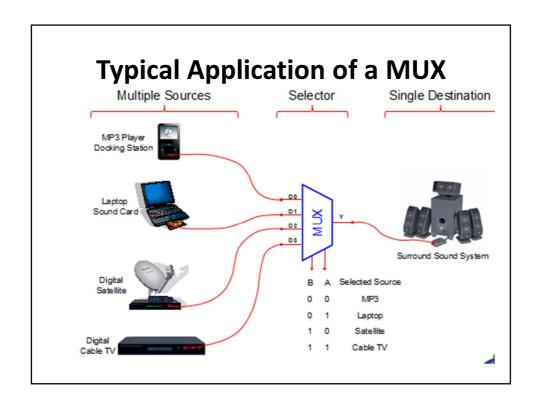

- 5. Give a practical application of Multiplexer circuits in Digital Electronics and Communications or Entertainment. Try to specify a MUX of specific size and provide the blueprint for your design.

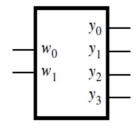

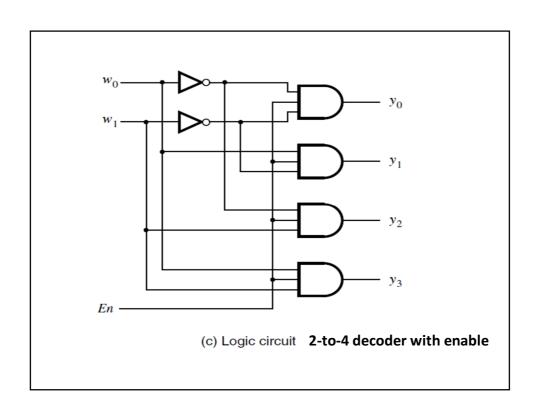

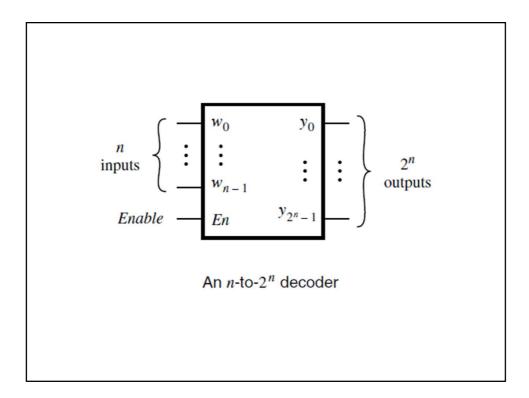

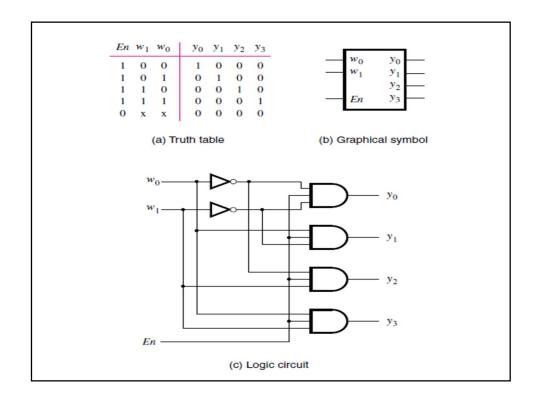

- **6.** State what is meant by a Decoder? Analyze the 2:4 Decoder with the aid of graphic symbol, truth table and logic circuit.

- 7. Analyze how the basic Decoder can be made more efficient by means of the Enable input. Draw the graphic symbol, truth table and logic circuit.

- **8.** Define the Demultiplexer function. Analyze the 1:8 DEMUX with the aid of graphic symbol, truth table and logic implementation. Give an application of this function.

- **9.** Implement the following Boolean function using an appropriate Multiplexer after judicious manipulation of the original truth table.

$$f = x \odot y \odot z$$

,

where  $\odot \rightarrow Ex-NOR$  function

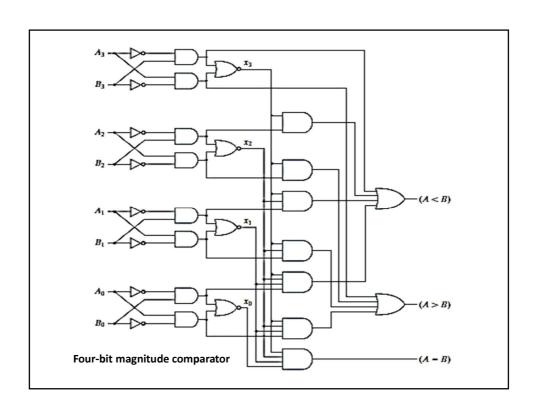

- **10.** State what is meant by a Magnitude Comparator? Analyze the 4-bit Magnitude Comparator with the aid of graphic symbol, truth table and logic circuit.

- **11.** Analyze the 3:8 Decoder by means of the graphic symbol, truth table and logic circuit. How would an extra enable input improve its robustness?

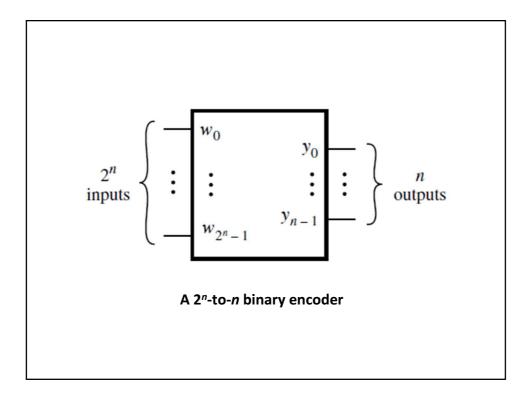

- **12.** State what is meant by Encoder? Analyze the 4:2 Encoder by means of the graphic symbol, truth table and logic circuit.

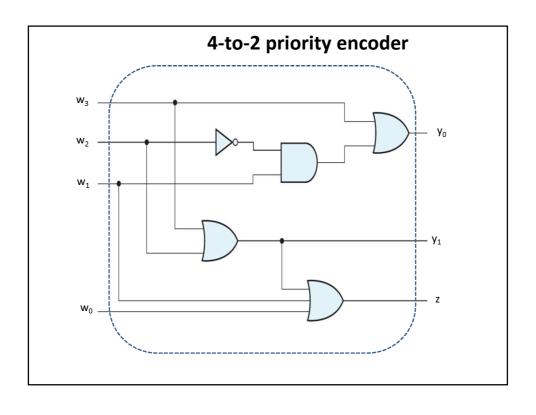

- **13.** Investigate the Priority Encoder circuit as an improvement over plain ol' Encoder with the aid of an example.

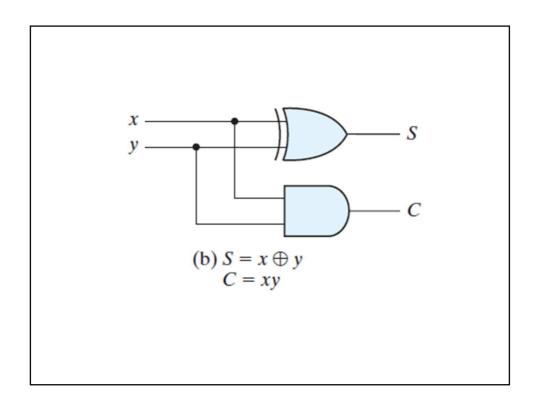

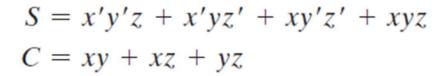

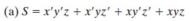

- **14.** Analyze the Full Adder and Half Adder with the aid of truth table and logic circuit diagram.

# Module-3 (Part-2)

- 1. Describe the BCD Adder with the help of Logic Diagram and Functional table of operation.

- 2. Analyze the Ripple Carry Adder with the help of Logic Diagram and Functional table of operation.

- **3.** Describe the Binary Subtractor with overflow detection with the help of Logic Diagram and operation. Also explain the detection of Overflow.

- **4.** Describe the Priority Encoder with the help of Logic Diagram and Functional table of operation

- **5.** Analyze the 4-bit Magnitude Comparator with the help of logic expressions, Logic Diagram and operational description.

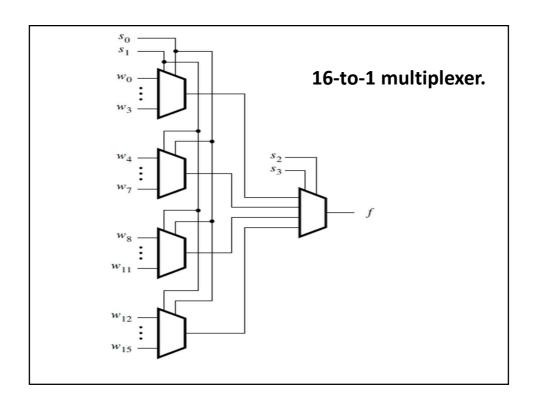

- 6. Analyze the 16:1 Multiplexer using the 4:1 Multiplexer with logic diagram and develop the Hierarchical Verilog Code for the 16:1 Multiplexer using functional description of 4:1 Multiplexer code. Describe the steps in arriving at the final code.

- 7. State what is meant by a Decoder? Analyze the 2:4 Decoder with the aid of graphic symbol, truth table and logic circuit.

- **8.** Analyze how the basic Decoder can be made more efficient by means of the Enable input. Draw the graphic symbol, truth table and logic circuit.

- 9. Analyze the 2:4 Decoder with the aid of truth table and logic diagram and develop the Verilog Code using case statement for the 2:4 Decoder system. Describe the steps in arriving at the final code.

- **10.** Use Verilog code to model a Full Adder system using Gate primitives, by starting with the logic diagram of a Full Adder.

- 11. Use Verilog code to model a 4-bit Binary Adder system using Gate primitives, by starting with the functional description of a Full Adder.

- 12. Use Verilog code to model a 4:1 MUX using Gate primitives, by starting with the logic diagram of a Full Adder.

- 13. Use Verilog code to model a 16:1 MUX using Hierarchical coding, by starting with the functional description of a 4:1 MUX.

- **14.** Use Verilog code to model a 2:4 Decoder using Gate primitives, by starting with the logic diagram.

- **15.** Use Verilog code to model a 2:4 Decoder in an alternative way using case statement along with Gate primitives, by starting with the logic diagram.

# **Module-4**

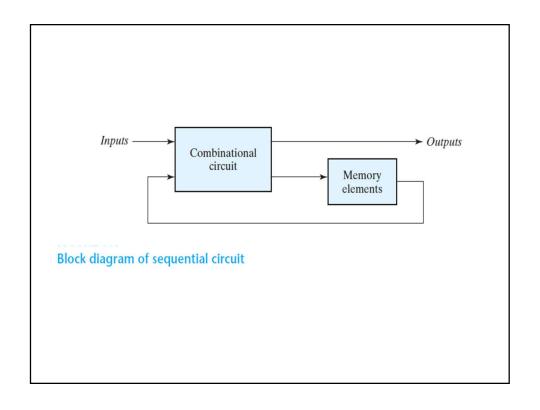

- 1. What is a Sequential system? With the aid of a block diagram, explain how a sequential circuit can be constructed.

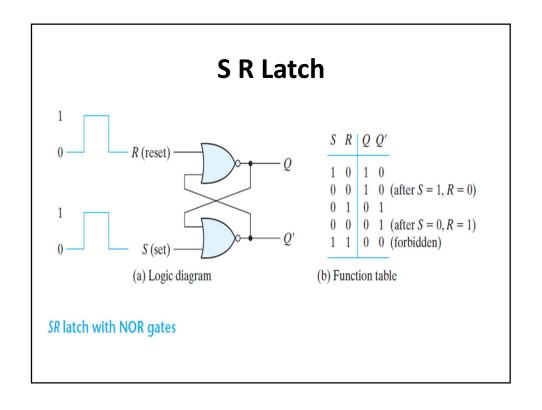

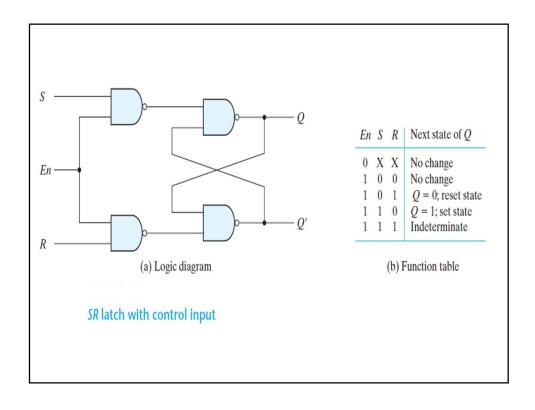

- 2. Analyze the S R Latch with the aid of Logic diagram and Functional table. How does the addition of an enable input make the latch operate with clock signal. What is the main drawback of this latch?

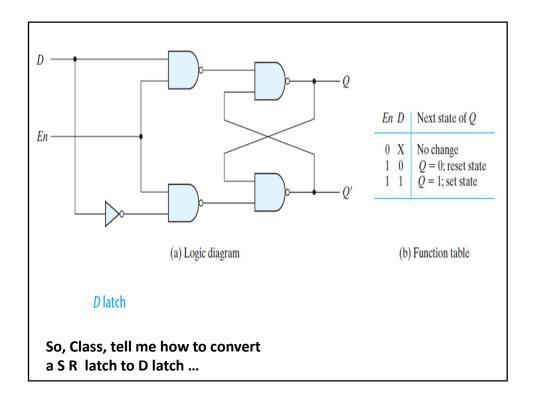

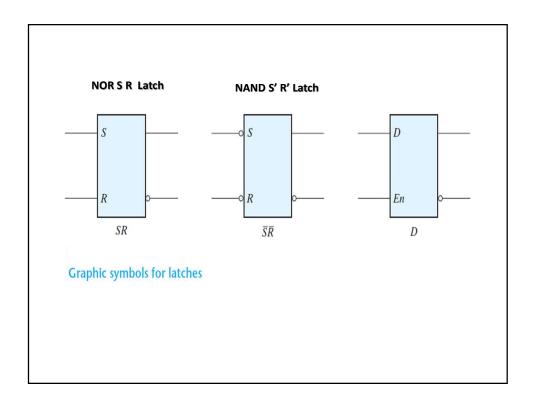

- **3.** Analyze the Transparent Latch with the aid of Logic diagram and Functional table. Represent the Graphic symbols for this latch.

- 4. Analyze the ET Flip Flop or MSD Flip Flop with the aid of Logic diagram and Functional table. Represent the Graphic symbols for this flip flop.

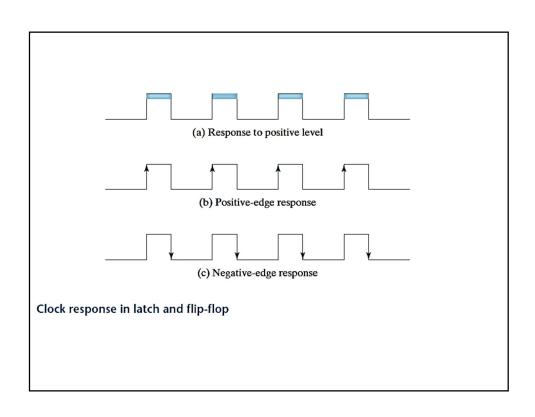

- 5. Compare and Contrast Latch and Flip Flop. With diagrams, dissect the structure of a periodic clock signal that caters for each of these.

- **6.** Describe the J-K Flip Flop with the aid of Logic Diagram and Functional table or Characteristic Table. Why is this called Universal Flip Flop?

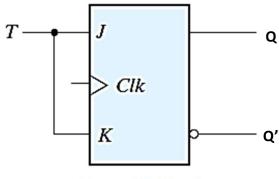

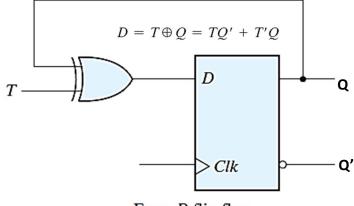

- 7. Describe the realization of T Flip Flop and D Flip Flop from the Universal Flip Flop, with clear reference to additional hardware requirements.

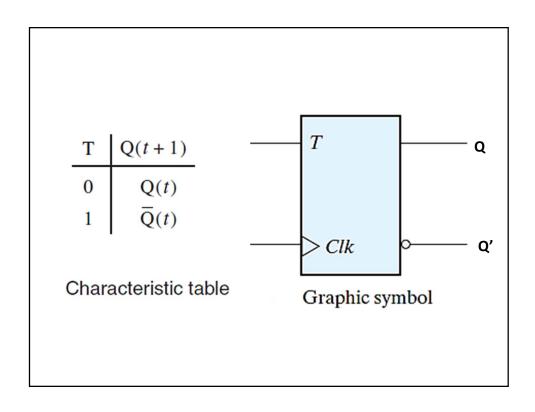

- **8.** Draw the Characteristic Tables, write down the characteristic equations and draw the Excitation Tables for the S-R, D, J-K and T flip flops.

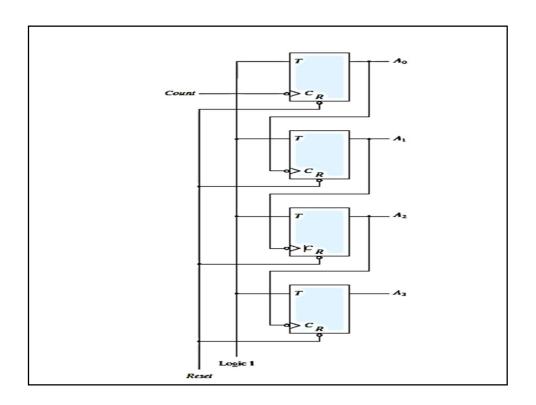

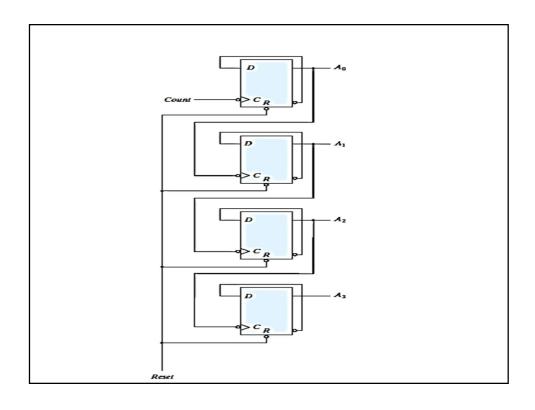

- **9.** Analyze the Binary Ripple Counter using D Flip Flops/ T Flip Flops and describe the operation with the aid of Count table.

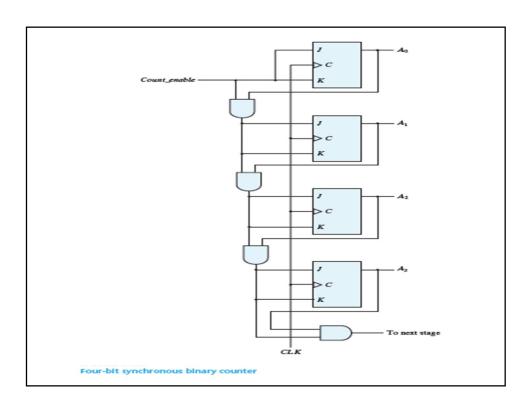

- **10.** Configure a 4-bit Synchronous Counter using J-K Flip Flops and provide the functional table, logic diagram, Count table and describe its operation. Compare with Ripple Counter of same capacity.

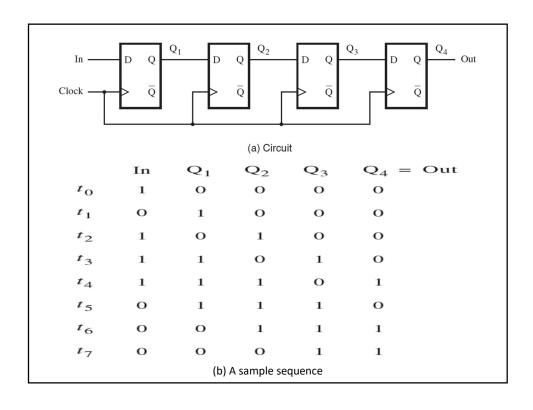

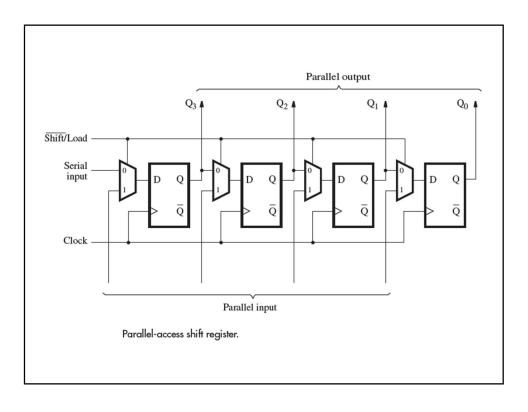

- 11. Configure a 4-bit Parallel Access Shift Register using D Flip- Flops and provide the functional table, logic diagram and describe its operation for the various modes such as SISO, SIPO, PISO and PIPO.

- **12.** Describe the Ring Counter and the Johnson Counter with the aid of Logic Diagram, Functional table and details of operation.

- **13.** Construct the hierarchical Verilog code for a 4-bit Shift Register with the help of functional code of D Flip Flop. Comment on the suitability of the code.

- **14.** Construct the Verilog code for an Up Counter. Comment on the suitability of the code.

**15.** Analyze the Verilog construct of use in Sequential circuits and construct the code for a D Flip Flop operating on the rising edge of the clock, with use of Asynchronous reset input. Comment on the sensitivity list.

# **Module-5**

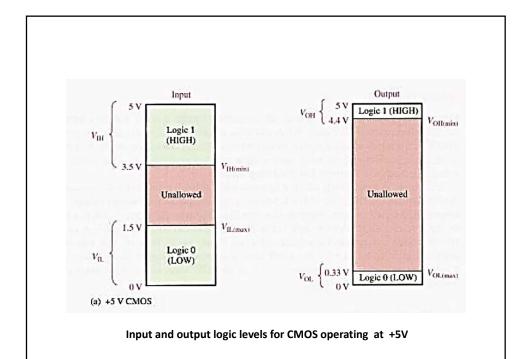

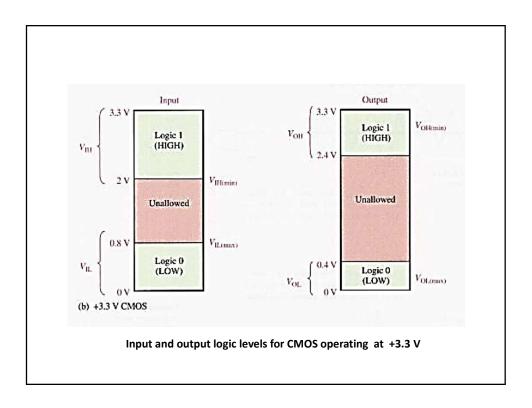

- 1. Analyze the CMOS Logic Levels for Input voltage and Output voltages with the aid of diagrams.

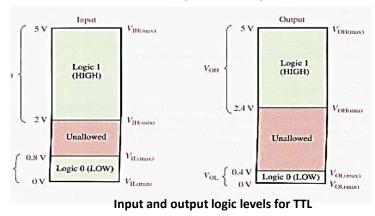

- 2. Analyze the TTL Logic Levels for Input voltage and Output voltages with the aid of diagrams.

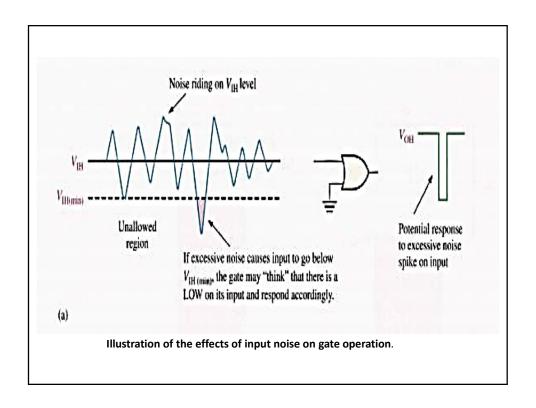

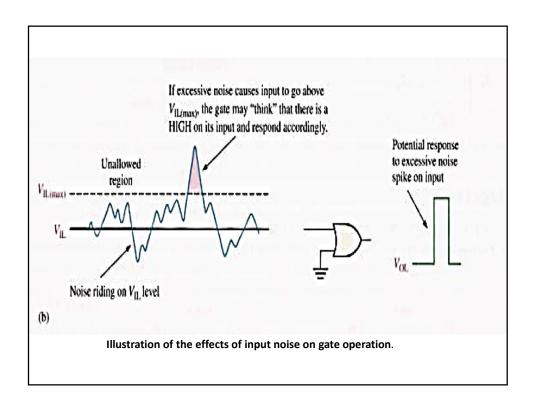

- 3. Justify the need for Noise Immunity in Digital Logic Systems.

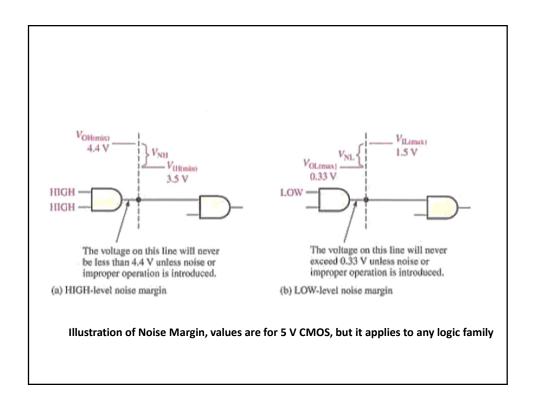

- **4.** Define Noise Margin. Explain the quantitative measures for Noise Margin with the aid of diagrams of CMOS 5 V family.

- **5.** Determine the High-level and LOW-level noise margins for CMOS and for TTL using their logic level voltage ranges. Which is preferable for a noise prone environment?

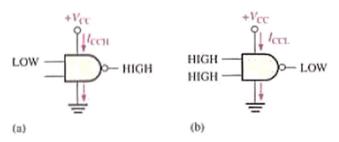

- **6.** Analyze the Power Dissipation in logic circuits and obtain quantitative measures of the same.

- 7. A certain gate draws 3  $\mu$ A when its output is HIGH and 4.6  $\mu$ A when its output is LOW. What is its average power dissipation if  $V_{cc}$  is 5 V and the gate is operated on a 50% duty cycle?

- 8. A certain IC gate has an  $I_{CCH} = 1.5 \mu A$  and  $I_{CCL} = 2.8 \mu A$ . Determine the average Power dissipation for 50% duty cycle operation if  $V_{cc}$  is 5 V.

- **9.** Analyze the Binary Ripple Counter using D Flip Flops/ T Flip Flops and describe the operation with the aid of Count table.

- 10. Compare and contrast the Power Dissipation in CMOS and TTL circuits.

- 11. Analyze the Propagation time Delay in Logic circuits and justify how the Speed-Power product can be used as a benchmark.

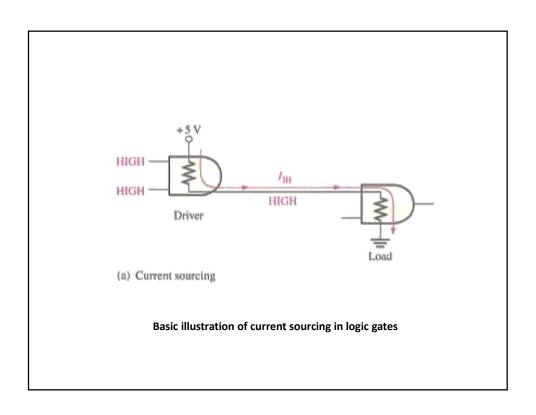

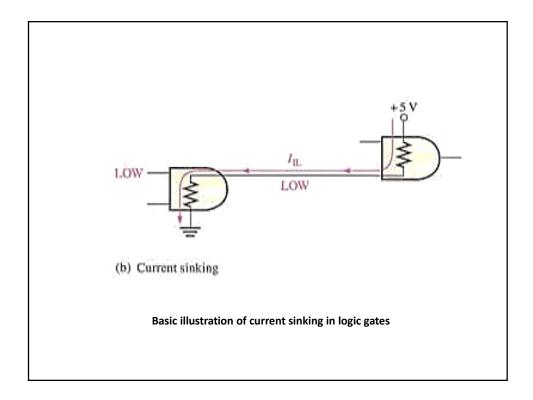

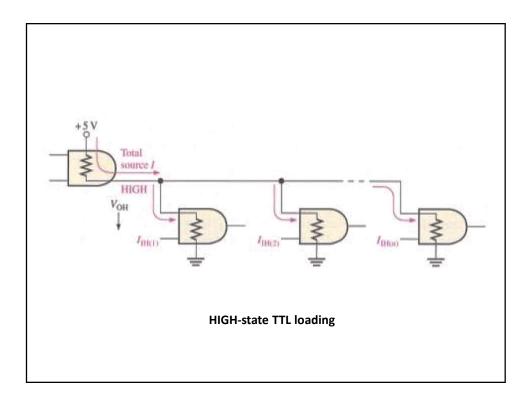

- **12.** Explain the Loading and Fan-out of the Gates. How does excessive loading affect the Noise Margin of the gates?

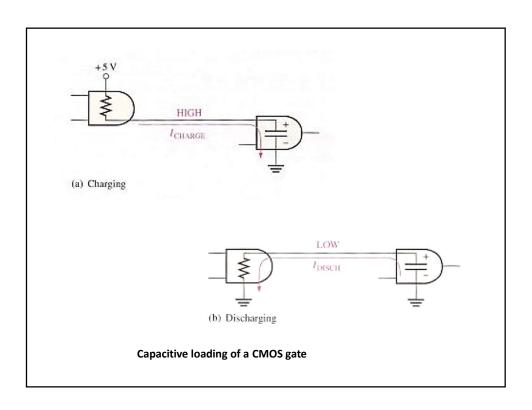

- 13. Describe the CMOS Loading with the help of diagrams.

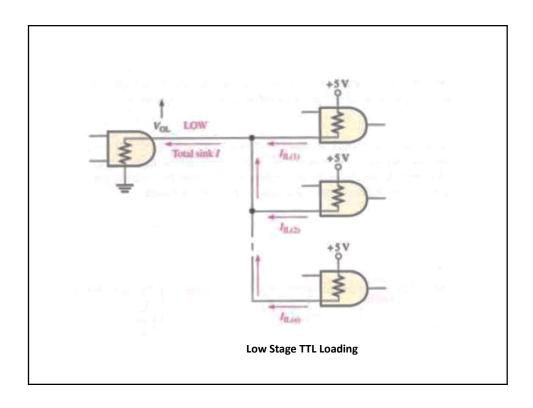

- **14.** Describe the TTL Loading with the help of diagrams.

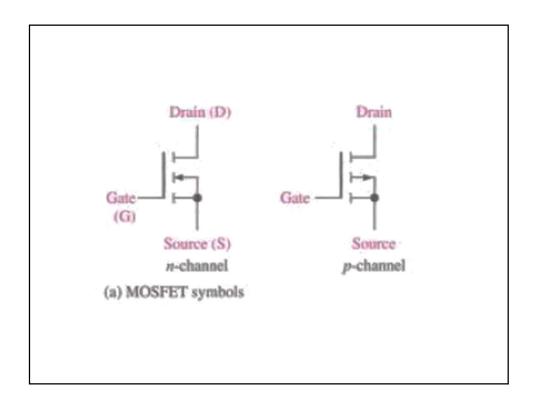

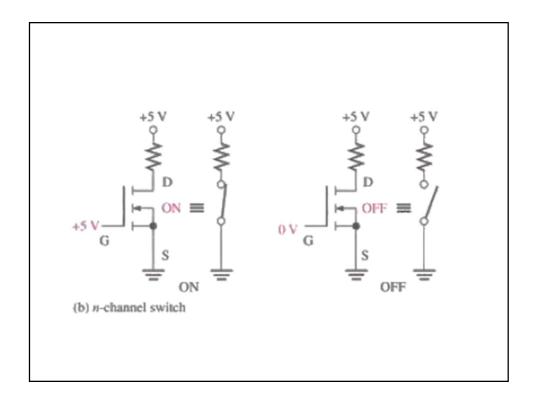

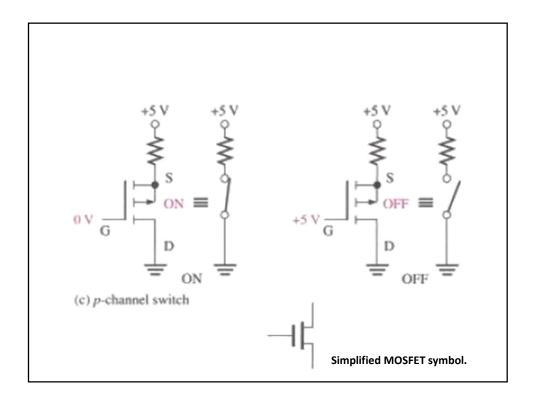

- **15.** Analyze the CMOS Inverter circuit with the aid of Circuit Diagram and Operational Diagrams.

- **16.** Analyze the TTL Inverter circuit with the aid of Circuit Diagram and Operational Diagrams.

- 17. Analyze the TTL NAND Gate circuit with the aid of Circuit Diagram and Operational Diagrams.

- **18.** Analyze the CMOS NAND gate circuit with the aid of Circuit Diagram and functional table and operation.

- **19.** Analyze the CMOS NOR gate circuit with the aid of Circuit Diagram and functional table and operation.

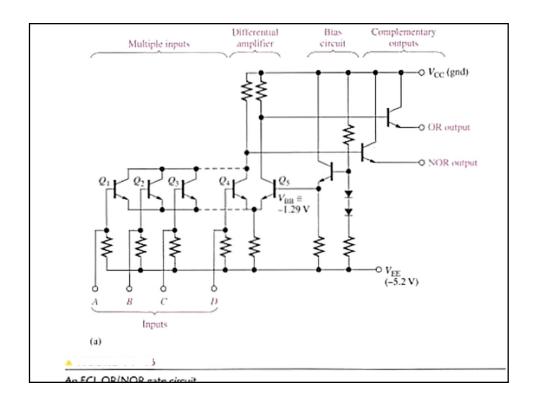

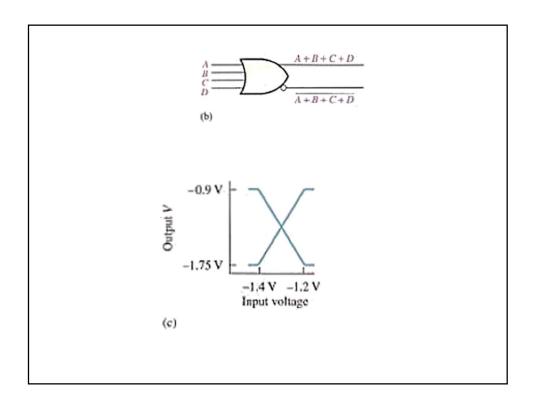

- 20. Explain the ECL Family of digital logic circuits.

- **21.** Analyze the ECL NOR/OR gate with the aid of circuit diagram, operation and transfer characteristic.

- **22.** Explain the Noise margin of ECL circuits.

- 23. Compare and contrast the ECL, CMOS and TTL family of logic gates.

#### ECT 203 LOGIC CIRCUIT DESIGN

This course aims to impart the basic knowledge of Logic Circuits and enable students to apply it to design a Digital System.

## Module – I: Number Systems and Codes:

#### Introduction

A digital computer stores data in terms of digits (numbers) and proceeds in discrete steps from one state to the next. The states of a digital computer typically involve binary digits which may take the form of the presence or absence of magnetic markers in a storage medium, on-off switches or relays. In digital computers, even letters, words and whole texts are represented digitally.

Digital Logic is the basis of electronic systems, such as computers and cell phones. Digital Logic is rooted in binary code, a series of zeroes and ones each having an opposite value. This system facilitates the design of electronic circuits that convey information, including logic gates. Digital Logic gate functions include and, or and not. The value system translates input signals into specific output. Digital Logic facilitates computing, robotics and other electronic applications.

Digital Logic Design is foundational to the fields of electrical engineering and computer engineering. Digital Logic designers build complex electronic components that use both electrical and computational characteristics. These characteristics may involve power, current, logical function, protocol and user input. Digital Logic Design is used to develop hardware, such as circuit boards and microchip processors. This hardware processes user input, system protocol and other data in computers, navigational systems, cell phones or other high-tech systems.

#### 1.2 NUMBER SYSTEMS

#### **Decimal Numbers**

A decimal number such as 7,392 represents a quantity equal to 7 thousands, plus 3 hundreds, plus 9 tens, plus 2 units. The thousands, hundreds, etc., are powers of 10 implied by the position of the coefficients (symbols) in the number. To be more exact, 7,392 is a shorthand notation for what should be written as:

$$7 \times 10^3 + 3 \times 10^2 + 9 \times 10^1 + 2 \times 10^0$$

However, the convention is to write only the numeric coefficients and, from their position, deduce the necessary powers of 10, with powers increasing from right to left. In general, a number with a decimal point is represented by a series of coefficients:

The coefficients aj are any of the 10 digits (0, 1, 2, ..., 9), and the subscript value j gives the place value and, hence, the power of 10 by which the coefficient must be multiplied.

So 7392 can be expanded with a3=7, a2=3, a1=9, and a0=2, and the other coefficients equal to zero.

The radix of a number system determines the number of distinct values that can be used to represent any arbitrary number. The decimal number system is said to be of base, or radix, 10 because it uses 10 digits and the coefficients are multiplied by powers of 10.

The radix point (e.g., the decimal point) distinguishes positive powers of 10 from negative powers of 10.

## **Binary Numbers**

The binary system is a different number system. The coefficients of the binary number system have only two possible values: 0 and 1. So the radix is 2. Each coefficient aj is multiplied by a power of the radix, for example,  $2^j$ , and the results are added to obtain the decimal equivalent of the number. The radix point or the binary point distinguishes positive powers of 2 from negative powers of 2.

For example, consider the binary number 11010.11<sub>2</sub>

Find the decimal equivalent of the binary number 11010.11<sub>2</sub>

11010.11<sub>2</sub> can be expanded as

$$1 \times 2^4 + 1 \times 2^3 + 0 \times 2^2 + 1 \times 2^1 + 0 \times 2^0 + 1 \times 2^{-1} + 1 \times 2^{-2} = 26.75_{10}$$

So 26.75<sub>10</sub> is the decimal equivalent of 11010.11<sub>2</sub>

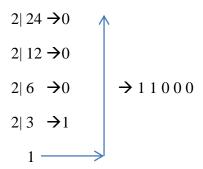

Given a decimal number, the binary equivalent can be found by repeatedly dividing by 2 and extracting the remainder of the series of divisions, till the quotient becomes 1 and then arrange the remainders from bottom to top.

For example, find the binary equivalent of 24<sub>10</sub>

Therefore,  $24_{10} \equiv 11000_2$

#### **Octal Numbers**

The octal system is a different number system. The coefficients of the octal number system have only eight possible values: 0, 1, 2, 3, 4, 5, 6 and 7. So the radix is 8. Each coefficient aj is multiplied by a power of the radix, for example, 8 <sup>j</sup>, and the results are added to obtain the

decimal equivalent of the number. The radix point or the octal point distinguishes positive powers of 8 from negative powers of 8.

For example, consider the octal number 1004.02<sub>8</sub>

Find the decimal equivalent of the octal number 1004.02<sub>8</sub>

$$1004.02_8$$

can be expanded as  $1 \times 8^3 + 0 \times 8^2 + 0 \times 8^1 + 4 \times 8^0 + 0 \times 8^{-1} + 2 \times 8^{-2} = 516.03125_{10}$

So  $516.03125_{10}$  is the decimal equivalent of  $1004.02_8$

The conversion between octal numbers and binary numbers is much simpler and faster to perform. Simply represent each octal digit as a combination of 3 binary digits or bits. Similarly to convert binary numbers to octal, group sets of 3 bits from the lsb to the msb. If you run out of bits add zeros from the msb.

| Octal | Bits |

|-------|------|

| Digit |      |

| 0     | 000  |

| 1     | 001  |

| 2     | 010  |

| 3     | 011  |

| 4     | 100  |

| 5     | 101  |

| 6     | 110  |

| 7     | 111  |

Example: Convert the octal number 7765431<sub>8</sub> to binary

Example: Convert the binary number 11000112 to octal

$$= 001 \ 100 \ 011$$

$$1 \quad 4 \quad 3 \quad \rightarrow 143$$

#### **Hexadecimal Numbers**

The hexadecimal system is a different number system. The coefficients of the hex number system have 16 possible values: 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E and F. So the radix is 16. Each coefficient aj is multiplied by a power of the radix, for example, 16 <sup>j</sup>, and the results are added to obtain the decimal equivalent of the number. The radix point or the hex point distinguishes positive powers of 16 from negative powers of 16.

For example, consider the hex number 100A<sub>16</sub>

Find the decimal equivalent of the hex number 100A<sub>16</sub>

$100A_{16}$  can be expanded as  $1\times16^3 + 0\times16^2 + 0\times16^1 + 10\times16^0 = 4106_{10}$

So 4106<sub>10</sub> is the decimal equivalent of 100A<sub>16</sub>

The conversion between hex numbers and binary numbers is much simpler and faster to perform. Simply represent each hex digit as a combination of 4 binary digits or bits. Similarly to convert binary numbers to hex, group sets of 4 bits from the lsb to the msb. If you run out of bits add zeros from the msb.

| Hexadecimal | Bits |

|-------------|------|

| Digit       |      |

| 0           | 0000 |

| 1           | 0001 |

| 2           | 0010 |

| 3           | 0011 |

| 4           | 0100 |

| 5           | 0101 |

| 6           | 0110 |

| 7           | 0111 |

| 8           | 1000 |

| 9           | 1001 |

| A           | 1010 |

| В           | 1011 |

| С           | 1100 |

| D           | 1101 |

| Е           | 1110 |

| F           | 1111 |

|             |      |

Example: Convert the HEX number ABCDE<sub>16</sub> to binary

msb lsb

$ABCDE_{16} = 1010\ 1011\ 1100\ 1101\ 1110 \equiv 1010101111100110111110_2$

Example: Convert the binary number 1100011<sub>2</sub> to hex

$$= 0000 \ 0110 \ 0011 \\ 0 \ 6 \ 3 \ \rightarrow 063_{16}$$

More examples:

```

100011001110_2 = 100\ 011\ 001\ 110_2 = 4316_8

1110110110101001_2 = 011\ 101\ 101\ 110\ 101\ 001_2 = 355651_8

```

The procedure for binary to hexadecimal conversion is similar, except we use groups of four bits:

```

100011001110_2 = 100011001110_2 = 8CE_{16}

11101101110101001_2 = 00011101101110101001_2 = 1DBA9_{16}

```

In these examples we have freely added zeroes on the left to make the total number of bits a multiple of 3 or 4 as required.

Table 1

Binary, decimal, octal, and hexadecimal numbers.

| Binary | Decimal | Octal | 3-Bit<br>String | Hexadecimal | 4-Bit<br>String |

|--------|---------|-------|-----------------|-------------|-----------------|

| 0      | 0       | 0     | 000             | 0           | 0000            |

| 1      | 1       | 1     | 001             | 1           | 0001            |

| 10     | 2       | 2     | 010             | 2           | 0010            |

| 11     | 3       | 3     | 011             | 3           | 0011            |

| 100    | 4       | 4     | 100             | 4           | 0100            |

| 101    | 5       | 5     | 101             | 5           | 0101            |

| 110    | 6       | 6     | 110             | 6           | 0110            |

| 111    | 7       | 7     | 111             | 7           | 0111            |

| 1000   | 8       | 10    | _               | 8           | 1000            |

| 1001   | 9       | 11    | _               | 9           | 1001            |

| 1010   | 10      | 12    | _               | Α           | 1010            |

| 1011   | 11      | 13    | _               | В           | 1011            |

| 1100   | 12      | 14    | _               | С           | 1100            |

| 1101   | 13      | 15    | _               | D           | 1101            |

| 1110   | 14      | 16    | _               | E           | 1110            |

| 1111   | 15      | 17    | _               | F           | 1111            |

If a binary number contains digits to the right of the binary point, we can convert them to octal or hexadecimal by starting at the binary point and working right. Both the left-hand and right-hand sides can be padded with zeroes to get multiples of three or four bits, as shown in the example below:

```

10.1011001011_2 = 010.101100101100_2 = 2.5454_8

= 0010.101100101100_2 = 2.B2C<sub>16</sub>

```

Converting in the reverse direction, from octal or hexadecimal to binary, is very easy. We simply replace each octal or hexadecimal digit with the corresponding 3- or 4-bit string, as shown below:

```

1357_8 = 001\ 011\ 101\ 111_2

2046.17_8 = 010\ 000\ 100\ 110\ .001\ 111_2

BEAD_{16} = 1011\ 1110\ 1010\ 1101_2

9F.46C_{16} = 1001\ 111\ .0100\ 0110\ 1100_2

```

The octal number system was quite popular 25 years ago because of certain minicomputers that had their front-panel lights and switches arranged in groups of three. However, the octal number system is not used much today, because of the preponderance of machines that process 8-bit *bytes*. It is difficult to extract individual byte values in multibyte quantities in the octal representation; for

example, what are the octal values of the four 8-bit bytes in the 32-bit number with octal representation 12345670123<sub>8</sub>?

In the hexadecimal system, two digits represent an 8-bit byte, and 2n digits represent an n-byte word; each pair of digits constitutes exactly one byte. For example, the 32-bit hexadecimal number 5678ABCD<sub>16</sub> consists of four bytes with values 56<sub>16</sub>, 78<sub>16</sub>, AB<sub>16</sub>, and CD<sub>16</sub>. In this context, a 4-bit hexadecimal digit is sometimes called a nibble; a 32-bit (4-byte) number has eight nibbles. Hexadecimal numbers are often used to describe a computer's memory address space. For example, a computer with 16-bit addresses might be described as having read/write memory installed at addresses 0–EFFF<sub>16</sub>, and read-only memory at addresses F000–FFFF<sub>16</sub>. Many computer programming languages use the prefix "0x" to denote a hexadecimal number, for example, 0xBFC0000.

# Table -2 Conversion methods for common radices.

| Conversion     | Method       | Example                                                                                                                                                                                                                                                          |

|----------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Binary to      |              |                                                                                                                                                                                                                                                                  |

| Octal          | Substitution | $10111011001_2 = 10 \ 111 \ 011 \ 001_2 = 2731_8$                                                                                                                                                                                                                |

| Hexadecimal    | Substitution | $10111011001_2 = 101 \ 1101 \ 1001_2 = 5D9_{16}$                                                                                                                                                                                                                 |

| Decimal        | Summation    | $10111011001_{2} = 101 \ 1101 \ 1001_{2} = 5D9_{16}$ $10111011001_{2} = 1 \cdot 1024 + 0 \cdot 512 + 1 \cdot 256 + 1 \cdot 128 + 1 \cdot 64$ $+ 0 \cdot 32 + 1 \cdot 16 + 1 \cdot 8 + 0 \cdot 4 + 0 \cdot 2 + 1 \cdot 1 = 1497_{10}$                             |

| Octal to       |              |                                                                                                                                                                                                                                                                  |

| Binary         | Substitution | $1234_8 = 001\ 010\ 011\ 100_2$                                                                                                                                                                                                                                  |

| Hexadecimal    | Substitution | $1234_8 = 001\ 010\ 011\ 100_2 = 0010\ 1001\ 1100_2 = 29C_{16}$                                                                                                                                                                                                  |

| Decimal        | Summation    | $1234_8 = 1 \cdot 512 + 2 \cdot 64 + 3 \cdot 8 + 4 \cdot 1 = 668_{10}$ How??                                                                                                                                                                                     |

| lexadecimal to |              |                                                                                                                                                                                                                                                                  |

| Binary         | Substitution | $C0DE_{16} = 1100\ 0000\ 1101\ 1110_2$                                                                                                                                                                                                                           |

| Octal          | Substitution | $CODE_{16} = 1100\ 0000\ 1101\ 1110_2 = 1\ 100\ 000\ 011\ 011\ 110_2 = 140$                                                                                                                                                                                      |

| Decimal        | Summation    | $C0DE_{16} = 12 \cdot 4096 + 0 \cdot 256 + 13 \cdot 16 + 14 \cdot 1 = 49374_{10}$                                                                                                                                                                                |

| Decimal to     |              |                                                                                                                                                                                                                                                                  |

| Binary         | Division     | $108_{10} \div 2 = 54 \text{ remainder 0}  (LSB)$ $\div 2 = 27 \text{ remainder 0}$ $\div 2 = 13 \text{ remainder 1}$ $\div 2 = 6 \text{ remainder 1}$ $\div 2 = 3 \text{ remainder 0}$ $\div 2 = 1 \text{ remainder 1}$ $\div 2 = 0 \text{ remainder 1}  (MSB)$ |

|                |              | $108_{10} = 1101100_2$                                                                                                                                                                                                                                           |

| Octal          | Division     | $108_{10} \div 8 = 13$ remainder 4 (least significant digit)<br>$\div 8 = 1$ remainder 5<br>$\div 8 = 0$ remainder 1 (most significant digit)<br>$108_{10} = 154_8$                                                                                              |

| Hexadecimal    | Division     | $108_{10} \div 16 = 6$ remainder 12 (least significant digit)<br>$\div 16 = 0$ remainder 6 (most significant digit)<br>$108_{10} = 6C_{16}$                                                                                                                      |

# **Arithmetic: Decimal Addition/Subtraction**

Use decimal number line:

ECT 203

```

0 1 2 3 4 5 6 7 8 9

```

```

0+1 = 1; 1+1 = 2; 2+1 = 3; 3+1 = 4; 4+1 = 5; 5+1 = 6; 6+1 = 7; 7+1 = 8; 8+1=9; 9+1=10

0+2 = 2; 1+4 = 5; 2+6 = 8; 3+5 = 8; 4+5 = 9; 5+2 = 7; 6+1 = 7; 7+2 = 9; 8+0=8; 9+2=11

```

Sample additions:

```

1 1

7920711.716+

234020.019

8154731.735

```

# **Arithmetic: Binary Addition/Subtraction**

Use binary number line:

```

0 1

0+1 = 1; 1+1 = 10; 10+1 = 11; 11+1 = 100;

1-1 = 0; 1-0 = 1; 11-1=10; 10-1=1; 0-1 = -1;

```

Sample additions:

# **Arithmetic: Octal Addition/Subtraction**

Use octal number line:

0 1 2 3 4 5 6 7

0+1=1; 1+1=2; 2+1=3; 3+1=4; 4+1=5; 5+1=6; 6+1=7; 7+1=10; 7+2=11; 7+3=12

0+2 = 2; 1+4 = 5; 2+6 = 10; 3+5 = 10; 4+5 = 11; 5+2 = 7; 6+1 = 7; 7+2 = 11; 11+7=20; 17+2=21

2-6 = -4; 3-5 = -2; 4-5 = -1; 5-2 = 3; 10-1 = 7; 11-2 = 7; 12-5=5;

Sample addition:

1 1 1 1 6720711.716+

234120.112

7155032.030

7133032.030

# **Arithmetic: Hex Addition/Subtraction**

Use hexadecimal number line:

0 1 2 3 4 5 6 7 8 9 A B C D E F

8 + 1 = 9; 9 + 1 = A; A + 1 = B; B + 1 = C; C + 1 = D; D + 1 = E; E + 1 = F; F + 1 = 10;

7 + 4 = B; 6 + 6 = C; 5 + 5 = A; 4 + 7 = B; F + 2 = 11; 6 + A = 10;

F-2 = D; F-4 = B; E-6 = 8; 3-F = -C; A-5 = 5;

Sample additions:

1 B920711.E1A+

234020.019

BB54731. E33

ABC.DEF+

012.347

ACF. 136

# **Representation of Negative Numbers**

# Signed-Magnitude Representation

In the *signed-magnitude system*, a number consists of a magnitude and a symbol indicating whether the magnitude is positive or negative. Thus, we interpret decimal numbers +98, -57, +123.5, and -13 in the usual way, and we also assume that the sign is "+" if no sign symbol is written. There are two possible representations of zero, "+0" and "-0", but both have the same value.

The signed-magnitude system is applied to binary numbers by using an extra bit position to represent the sign (the sign bit). Traditionally, the most significant bit (MSB) of a bit string is used as the sign bit (0 = plus, 1 = minus), and the lower-order bits contain the magnitude. Thus, we can write several 8-bit signed-magnitude integers and their decimal equivalents:

$$01010101_2 = +85_{10}$$

$11010101_2 = -85_{10}$

$01111111_2 = +127_{10}$   $11111111_2 = -127_{10}$

$00000000_2 = +0_{10}$   $10000000_2 = -0_{10}$

The signed-magnitude system has an equal number of positive and negative integers. An *n*-bit signed-magnitude integer lies within the range  $-(2^{n-1}-1)$  through  $+(2^{n-1}-1)$ , and there are two possible representations of zero.

Practical design of digital logic circuit to add/sub signed magnitude numbers is complicated and is seldom undertaken.

# **One's (1's) Complement representation:**

The diminished radix-complement system for binary numbers is called the *ones'* complement. the most significant bit is the sign, 0 if positive and 1 if negative. Thus there are two representations of zero, positive zero  $(00\cdots00)$  and negative zero  $(11\cdots11)$ . Positive number representations are the same for both ones' and two's complements. However, negative number representations differ by 1. A weight of  $-(2^{n-1}-1)$ , rather than  $-2^{n-1}$ , is given to the most significant bit when computing the decimal equivalent of a ones'-complement number. The range of representable numbers is  $-(2^{n-1}-1)$  through  $+(2^{n-1}-1)$ . Some 8-bit numbers and their ones' complements are shown below:

$$17_{10} = 00010001_{2}$$

$-99_{10} = 10011100_{2}$   $\Downarrow$   $11101110_{2} = -17_{10}$   $01100011_{2} = 99_{10}$

$119_{10} = 01110111_{2}$   $-127_{10} = 10000000_{2}$   $\Downarrow$   $01111111_{2} = 127_{10}$

$0_{10} = 00000000_{2}$  (positive zero)

$0_{10} = 00000000_{2}$  (positive zero)

$0_{10} = 01111111_{2} = 0_{10}$  (negative zero)

The main advantages of 1's complement are its symmetry and ease of implementation. But the adder design for 1's complement numbers is not easy. Also zero detectors in a 1's complement system must check for both representations of zero, or must always convert 11...11 to 00...00.

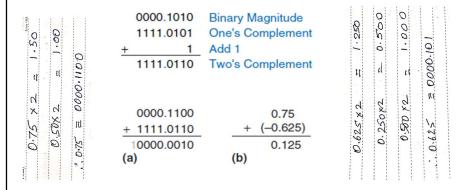

# Two's (2's) Complement representation:

For binary numbers, the radix complement is called the *two's complement*. The MSB of a number in this system serves as the sign bit; a number is negative if and only if its MSB is 1. The decimal equivalent for a two's-complement binary number is computed the same way as for an unsigned number, except that the weight of the MSB is  $-2^{n-1}$  instead of  $+2^{n-1}$ . The range of representable numbers is  $-(2^{n-1})$  through  $+(2^{n-1}-1)$ . Some 8-bit examples are shown below:

$$0_{10} = 00000000^2$$

$-128_{10} = 10000000^2$  complement bits  $01111111$   $01111111$   $-1$   $10000000^2$   $-128_{10} = 10000000^2$   $-128_{10} = 10000000^2$   $-128_{10} = 10000000^2$

A carry out of the MSB position occurs in one case,

in all two's-complement operations, this bit is ignored and only the low-order *n* bits of the result are used.

In the two's-complement number system, zero is considered positive because its sign bit is 0. Since two's complement has only one representation of zero, we end up with one extra negative number,  $-(2^{n-1})$ , that doesn't have a positive counterpart.

2's Complement numbers support sign extension. Most modern computers incorporate 2's complement system for subtraction.

# Exercise!!!

- 1. Subtract 5 from 17 using 8-bit signed numbers in 2's complement representation. Validate ur answer.

- Sol:

```

17: 0 0010001+

```

+5: 0 0000101

-5: 1 1111010 (1's Complement) 1 1 1 11010+

1

-5: 1 1 1 1 1011 (2's Complement)

1 00001100 (+17 + -5)

$00001100 \rightarrow +12$

\* 2. Subtract 17 from 16 using 8-bit 2s' complement representation and validate ur answer.

# **Binary Coded Decimal Codes**

- Binary numbers or bits are most suited for internal computations of digital systems.

- But humans prefer decimal numbers (Why?)

- So, external interfaces of digital system may read or display decimal numbers.

- Also some digital devices process decimal numbers directly.

- So, to do this, a decimal digit is represented by a string of bits.

- Different combinations of bit values in the string represent different decimal digits.

- For example, using a 4-bit string, we represent decimal  $0 \rightarrow 0000$ ,  $1 \rightarrow 0001$ ,  $2 \rightarrow 0010$ , and so on.

- Code is defined as a set of n-bit strings in which diff string patterns represent diff numbers or other things.

- Code word is a particular combination of n-bit string value.

- There <u>may or may not be</u> an arithmetic relationship between the code word and the thing it represents.

- A Code that uses n-bit strings <u>need not</u> contain 2<sup>n</sup> valid code words.

# (8421) BCD

- Binary Coded Decimal (BCD) encodes the digits 0 thro'

9 by their 4-bit unsigned bin representations 0000 thro' 1001.

- The code words 1010 thro' 1111 are not used.

- BCD is a <u>weighted code</u> as each decimal digit can be obtained from its code word by putting a fixed weight (2<sup>3</sup>=8, 2<sup>2</sup>=4, 2<sup>1</sup>=2,2<sup>0</sup>=1) for each code word bit.

- Place 2 BCD Digits in one 8-bit byte in <u>Packed BCD</u> representation.

- So one byte represents values from 0 to 99 in packed BCD repr as opposed to 0 to 255 for unsigned 8-bit binary num.

- BCD numbers with any desired number of digits can be got by using one byte for each two digits.

| Decimal digit | BCD (8421) |

|---------------|------------|

| o             | 0000       |

| 1             | 0001       |

| 2             | 0010       |

| 3             | 0011       |

| 4             | 0100       |

| 5             | 0101       |

| 6             | 0110       |

| 7             | 0111       |

| 8             | 1000       |

| 9             | 1001       |

|               |            |

|               | 1010       |

|               | 1011       |

|               | 1100       |

| 23            | 1101       |

|               | 1110       |

|               | 1111       |

# **Negative BCD numbers**

- Signed BCD numbers have <u>one extra digit</u> <u>position</u> (4-bits) for the sign.

- Both the signed-magnitude and 10's complement representations are used.

- In signed-magnitude repr, the encoding of the sign bit is arbitrary.

- In 10's complement,  $+ \rightarrow 0000$ ,  $\rightarrow 1001$

# Additions of BCD digits (Use correction of 6)

# **2421 Code**

- This is also a <u>weighted code</u> having weights 2,4,2 and 1 for the code word bits from msb.

- The advantage of this code is that it is <u>self-complementing</u>, i.e., the code word for the 9's complement can be got by flipping the individual bits of the code word.

| Decimal digit | BCD (8421) | 2421 |

|---------------|------------|------|

| o             | 0000       | 0000 |

| 1             | 0001       | 0001 |

| 2             | 0010       | 0010 |

| 3             | 0011       | 0011 |

| 4             | 0100       | 0100 |

| 5             | 0101       | 1011 |

| 6             | 0110       | 1100 |

| 7             | 0111       | 1101 |

| 8             | 1000       | 1110 |

| 9             | 1001       | 1111 |

|               | 1010       | 0101 |

|               | 1011       | 0110 |

|               | 1100       | 0111 |

|               | 1101       | 1000 |

|               | 1110       | 1001 |

|               | 1111       | 1010 |

# **Excess-3 Code**

- This is an <u>unweighted</u> code.

- The code word for a decimal digit is got by adding 0011<sub>2</sub> to the corresponding BCD code word.

- As the code words follow a standard binary counting sequence, <u>standard binary counters</u> can easily be made to count in excess-3 code.

- This is also a <u>self-complementing</u> code.

|               | Decimal cod |        |                   |  |

|---------------|-------------|--------|-------------------|--|

| Decimal digit | BCD (8421)  | 2421   | Excess-3          |  |

| 0             | 0000        | 0000   | 0011              |  |

| 1             | 0001        | 0001   | 0100              |  |

| 2             | 0010        | 0010   | 0101              |  |

| 3             | 0011        | 0011   | 0110              |  |

| 4             | 0100        | 0100   | 0111              |  |

| 5             | 0101        | 1011   | 1000              |  |

| 6             | 0110        | 1100   | 1001              |  |

| 7             | 0111        | 1101   | 1010              |  |

| 8             | 1000        | 1110   | 1011              |  |

| 9             | 1001        | 1111   | 1100              |  |

|               |             | Unused | Unused code words |  |

|               | 1010        | 0101   | 0000              |  |

|               | 1011        | 0110   | 0001              |  |

|               | 1100        | 0111   | 0010              |  |

|               | 1101        | 1000   | 1101              |  |

|               | 1110        | 1001   | 1110              |  |

|               | 1111        | 1010   | 1111              |  |

# **Gray Code**

- A Digital Code in which there is <u>only one bit</u> <u>changes</u> between a pair of successive code words is called a Gray Code.

- Eg. 3-bit Gray code •

Is Gray Code a Weighted code?

| Decimal<br>number | Binary<br>code | Gray<br>code<br>000 |  |

|-------------------|----------------|---------------------|--|

| 0                 | 000            |                     |  |

| 1                 | 001            | 001                 |  |

| 2                 | 010            | 011                 |  |

| 3                 | 011            | 010<br>110<br>111   |  |

| 4                 | 100            |                     |  |

| 5                 | 101            |                     |  |

| 6                 | 110            | 101<br>100          |  |

| 7                 | 111            |                     |  |

# Represent 4-bit Gray Code...

Gray Code

| Gray<br>Code | Decimal<br>Equivalent |

|--------------|-----------------------|

| 0000         | 0                     |

| 0001         | 1                     |

| 0011         | 2                     |

| 0010         | 3                     |

| 0110         | 4                     |

| 0111         | 5                     |

| 0101         | 6                     |

| 0100         | 7                     |

| 1100         | 8                     |

| 1101         | 9                     |

| 1111         | 10                    |

| 1110         | 11                    |

| 1010         | 12                    |

| 1011         | 13                    |

| 1001         | 14                    |

| 1000         | 15                    |

- The Gray code is used in applications where normal sequence of binary number generated by hardware <u>produce an error</u> during transition from one number to the next.

- If binary numbers are used, a change from 0111 to 1000 may produce an <u>intermediate</u> <u>error</u> number 1001, if lsb takes longer to change than do the values of the other three bits.

- This could have <u>serious issues</u> for the machine.

- The Gray code eliminates this problem, since only one bit changes its value during any transition between two numbers.

# **ASCII Character Code**

- An alphanumeric character code is a set of code words that encodes the 10 decimal digits, the 26 letters of the alphabet, and a number of special characters.

- Such a set contains between 64 and <u>128</u> elements if both uppercase and lowercase letters are included, we need a binary code word of seven bits. (Why? → using 7 bit can repr [0-2<sup>7</sup>-1]→[0 to 127] = 128 combinations)

- The standard binary code for the alphanumeric characters is the *American Standard Code for Information Interchange* (ASCII), which uses 7 bits to code 128 characters.

|                | $b_7b_6b_5$ |     |     |     |     |              |     |     |

|----------------|-------------|-----|-----|-----|-----|--------------|-----|-----|

| $b_4b_3b_2b_1$ | 000         | 001 | 010 | 011 | 100 | 101          | 110 | 111 |

| 0000           | NUL         | DLE | SP  | 0   | @   | P            | `   | p   |

| 0001           | SOH         | DC1 | !   | 1   | Α   | Q            | a   | q   |

| 0010           | STX         | DC2 | **  | 2   | В   | R            | b   | r   |

| 0011           | ETX         | DC3 | #   | 3   | C   | S            | c   | S   |

| 0100           | EOT         | DC4 | \$  | 4   | D   | T            | d   | t   |

| 0101           | <b>ENQ</b>  | NAK | %   | 5   | E   | U            | e   | u   |

| 0110           | ACK         | SYN | &   | 6   | F   | V            | f   | v   |

| 0111           | BEL         | ETB | 4   | 7   | G   | W            | g   | w   |

| 1000           | BS          | CAN | (   | 8   | H   | $\mathbf{X}$ | h   | x   |

| 1001           | HT          | EM  | )   | 9   | I   | Y            | i   | у   |

| 1010           | LF          | SUB | *   | :   | J   | Z            | j   | Z   |

| 1011           | VT          | ESC | +   | ;   | K   | [            | k   | {   |

| 1100           | FF          | FS  | ,   | <   | L   | ١            | 1   | ĺ   |

| 1101           | CR          | GS  | _   | =   | M   | 1            | m   | }   |

| 1110           | SO          | RS  |     | >   | N   | ۸            | n   | ~   |

| 1111           | SI          | US  | 1   | ?   | O   | _            | 0   | DEL |

| Control Characters |                     |     |                           |  |  |

|--------------------|---------------------|-----|---------------------------|--|--|

| NUL                | Null                | DLE | Data-link escape          |  |  |

| SOH                | Start of heading    | DC1 | Device control 1          |  |  |

| STX                | Start of text       | DC2 | Device control 2          |  |  |

| ETX                | End of text         | DC3 | Device control 3          |  |  |

| EOT                | End of transmission | DC4 | Device control 4          |  |  |

| ENQ                | Enquiry             | NAK | Negative acknowledge      |  |  |

| ACK                | Acknowledge         | SYN | Synchronous idle          |  |  |

| BEL                | Bell                | ETB | End-of-transmission block |  |  |

| BS                 | Backspace           | CAN | Cancel                    |  |  |

| HT                 | Horizontal tab      | EM  | End of medium             |  |  |

| LF                 | Line feed           | SUB | Substitute                |  |  |

| VT                 | Vertical tab        | ESC | Escape                    |  |  |

| FF                 | Form feed           | FS  | File separator            |  |  |

| CR                 | Carriage return     | GS  | Group separator           |  |  |

| SO                 | Shift out           | RS  | Record separator          |  |  |

| SI                 | Shift in            | US  | Unit separator            |  |  |

| SP                 | Space               | DEL | Delete                    |  |  |

# **Error-Detecting Code**

- To detect errors in data communication and processing, an <u>eighth bit</u> is sometimes added to the ASCII character to indicate its parity.

- A parity bit is an <u>extra bit</u> included with a message to make the total number of 1's either even or odd.

- Consider the following two characters and their even and odd parity:

ASCII A = 1000001 With even parity 01000001 11000001 1100100 01010100

# Parity bit -Error Detection

- Insert an extra bit in leftmost position of code to produce an even no: of 1's in character for even parity or an odd number of 1's in character for odd parity.

- In general, one or the other parity is used, with even parity being more common.

- Parity bit is helpful in detecting errors during transmission of info from one location to another.

- This function is handled by generating an even parity bit at the sending end for each character.

- The <u>eight-bit characters</u> that include parity bits are transmitted to their destination.

- The parity of each character is then checked at the receiving end.

- If the parity of the received character is not even, then at least <u>one</u> <u>bit</u> has changed value during the transmission.

- This method detects <u>one</u>, <u>three</u>, <u>or any odd combination of errors</u> in each character that is transmitted.

- An even combination of errors, however, goes <u>undetected</u>, and additional error detection codes may be needed to take care of that possibility.

### **Basics of Error Correction**

- After an error is detected, need to correct it!

- Make request for retransmission of the message on the assumption that the error was random and will not occur again.

- If the receiver detects a parity error, it sends back the ASCII NAK (negative acknowledge) control character consisting of an even parity eight bits 10010101.

- If no error is detected, the receiver sends back an ACK (acknowledge) control character, namely, 00000110.

### **Basics of Error Correction**

- The sending end will respond to an NAK by transmitting the message again until the correct parity is received.

- If, after a number of attempts, the transmission is still in error, a message can be sent to the operator to check for <u>malfunctions</u> in the transmission path.

# Introduction to Verilog programming...

- verilog HDL(Hardware Description Language)

was invented by Phil Moorby and Prabhu Goel

around 1984.

- It served as a proprietary hardware modeling language owned by Gateway Design Automation Inc. ...

- In 2001, extensions to **Verilog-**95 were submitted back to IEEE and became IEEE standard 1364-2001, known as **Verilog-**2001.

- In 1990, Gateway Design Automation Inc. was acquired by Cadence Design System, which is now one of the biggest suppliers of electronic design technologies and engineering services in the electronic design automation (EDA) industry.

- Cadence recognized the value of Verilog, and realized that if Verilog remained as a closed language, the pressure of standardization would eventually drive people to shift to VHDL.

- So in 1991 the **Open Verilog International** (OVI) (now known as **Accellera**) was organized by Cadence and the documentation of Verilog was transferred to public domain under the name of OVI.

- It was later submitted to IEEE and became IEEE standard 1364-1995, commonly referred as Verilog-95.

Verilog of the 20th Century ....

- In 2001, extensions to Verilog-95 were submitted back to IEEE and became IEEE standard 1364-2001, known as Verilog-2001.

- The extensions covered some deficiencies that users had found in Verilog-95.

- One of the most significant upgrades was that signed variables (in 2's complement) became supported.

- **Verilog-2001** is now dominant edition of Verilog supported by most design tools.

- In 2005, Verilog-2005 (IEEE Standard 1364-2005) was published with minor corrections and modifications.

- Also in 2005 **System Verilog**, a superset of **Verilog-2005**, with many new features and capabilities to aid design verification, was published.

- As of 2009, System Verilog and Verilog language standards were merged into System Verilog 2009 (IEEE Standard 1800-2009), which is one of the most popular languages for IC design and verification today.

- Xilinx® Vivado Design Suite, released in 2013, can support System Verilog for FPGA design and verification.

- At our famed worthy NCERC Labs, we are devout followers of the same...

Verilog of the 21st Century ....

### **Comments**

- A single line comment starts with // and tells

Verilog compiler to treat everything after this point to the end of the line as a comment.

- A multiple-line comment starts with /\* and ends with \*/ and cannot be nested.

### **Data Types**

- Verilog has two main groups of data types: the *variable* data type and the *net* data type.

- These two groups differ in the way that they are assigned and hold values.

- They also represent different hardware structures.

- The *net* data types can represent physical connections between structural entities, such as gates.

- Generally, it does not store values.

- Instead, its value is determined by the values of its drivers, such as a continuous assignment or a gate.

- A very popular *net* data type is the **wire**.

- There are also several other predefined data types that are part of nets.

- Examples are **tri** (for tri-state), **wand** (for wired and), **wor** (for wired or).

### The *variable* data type

- The *variable* data type is an abstraction of a data storage element.

- A variable shall store a value from one assignment to the next.

- An assignment statement in a procedure acts as a trigger that changes the value in the data storage element.

- A very popular variable data type is the reg.

- There are also several other predefined data types that are part of *variables*.

- Examples are reg, time, integer, real, and realtime.

### **Predefined Types**

nets connections between hardware elements

(declared with keywords such as wire)

variables data storage elements that can retain values

(declared with the keywords such as reg)

integer an integer is a variable data type

(declared with the keyword integer)

real real number constants and real variable data types for floating-point

number (declared with the keyword real)

time a special variable data type to store time information

(declared with the keyword time)

vectors wire or reg data types can be declared as vectors (multiple bits)

(vectors can be declared with [range1 : range2])

### **IEEE Standard**

- In previous versions of the Verilog standard, the term **register** was used to encompass the **reg**, **integer**, **time**, **real**, and **realtime** types.

- But starting with the 2005 IEEE 1364 Standard, that term is no longer used as a Verilog data type.

- A net or reg declaration without a range specification shall be considered 1 bit wide and is known as a scalar.

- Multiple bit net and reg data types shall be declared by specifying a range, which is known as a vector.

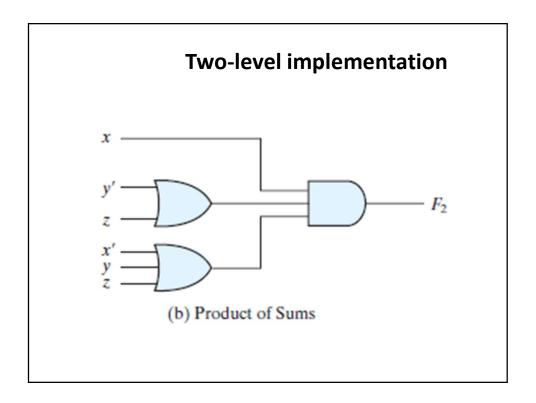

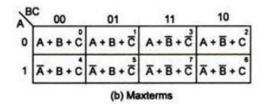

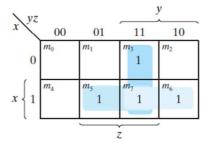

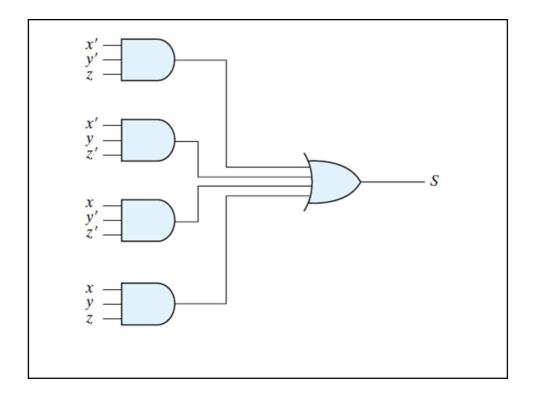

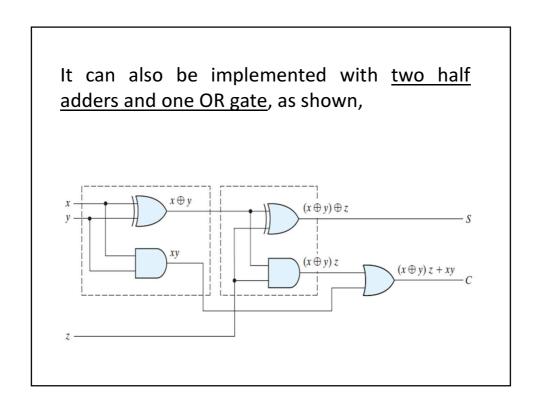

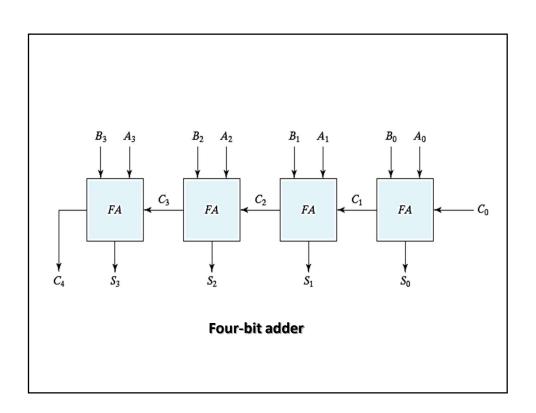

# **Verilog Operators**